滤波器是一种用来消除干扰杂讯的器件,可用于对特定频率的频点或该频点以外的频率进行有效滤除。它在电子领域中占有很重要的地位,在信号处理、抗干扰处理、电力系统、抗混叠处理中都得到了广泛的应用。而对于程控滤波器,该系统的最大特点在于其滤波模式可以程控选择,且-3dB截止频率程控可调,相当于一个集多功能于一体的滤波器,将有更好的应用前景。此外,系统具有幅频特性测试的功能,并通过示波器显示频谱特性,可直观地反应滤波效果。

1方案论证与选择

1.1可变增益放大模块的设计与论证

方案1:数字电位器控制两级INA129级联。用FPGA控制数字电位器DS1267使其输出不同的阻值,作为高精度仪表放大器INA129的反馈电阻。通过控制数字电位器来改变INA129的放大倍数,从而实现放大器的增益可调。

方案2:采用可变增益放大器AD603实现。可变增益放大器内部由R-2R梯形电阻网络和固定增益放大器构成,加在其梯型网络输入端的信号经衰减后,由固定增益放大器输出,衰减量是由加在增益控制接口的参考电压决定;可通过单片机控制,由DAC产生精确的参考电压控制增益,从而实现较精确的数控。

由于输入的正弦小信号振幅10mV,电压增益60dB,10dB步进程控可调,且电压增益误差不能大于5%。对精度而言两个方案都可实现,在AD603后再加一级放大也可实现60dB的放大倍数。但数字电位器内部结构复杂,有电容影响,后级接运放后会带来意想不到的后果,因此采用方案2。

1.2滤波器模块的设计与论证

方案1:采用数字滤波器。利用MATLAB的数字滤波器设计FIR或者IIR滤波器。数字滤波器具有精度高,截止特性好等优点。但是FIR滤波器会占用太多FPGA资源,IIR滤波器设计时工作量大且稳定性不高,且要使截止频率可调,必须使用不同的参数,设计起来软件量比较大。

方案2;采用无源LC滤波器。利用电感和电容可以搭建各种类型的滤波器。参照滤波器设计手册上的相关参数,可以比较容易地设计出理想的滤波器。但是如果要截止频率可调,只有改变电感电容参数,硬件会非常复杂。

方案3:采用集成的开关电容滤波器芯片。开关电容滤波器是由MOS开关、MOS电容和MOS运算放大器构成的一种大规模集成电路滤波器。其开关电容组在时钟频率的驱动下,可以等效成一个和时钟频率有关的等效电阻。当用外部时钟改变时,等效电阻改变,从而改变了滤波器的时间常敦,也就改变了滤波特性。开关电容滤波器可以直接处理模拟信号,而不必像数字滤波器那样需要A/D、D/A变换,简化了电路设计,提高了系统的可靠性。

综上所述,本系统采用方案3,利用集成芯片MAX297实现低通滤波器,利用LTC1068实现高通滤波器;采用方案2,利用无源LC滤波器技术来实现四阶椭圆低通滤波器。

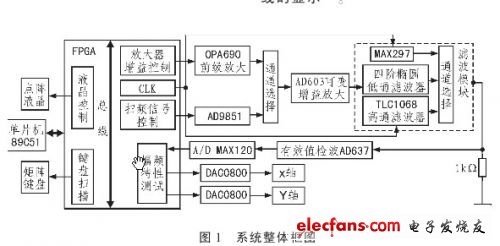

2系统总体设计方案及实现方框图

本系统以单片机及FPGA为控制核心,由可控增益放大模块、程控滤波模块和幅频特性测试模块构成。系统框图如图1所示。输入振幅为1V的信号经分压网络衰减后变成振幅10mV的小信号,经OPA690前级放大2倍,同时起到阻抗变换和隔离的作用。与此同时由AD9851产生一设定频率的正弦信号,通过模拟开关选择一道送到后级。信号由程序控制AD603进行0~60dB的可调增益放大后,送入滤波模块。滤波模块包括低通、高通、椭圆滤波器,其中低通、高通由程序控制-3dB截止频率在1~30kHz范围内可调,步进1kHz。椭圆滤波器截止频率50kHz。再通过模拟开关选择某一特定滤波信号输出,经有效值检波和A/D转换后送入FPGA进行幅频特性的测试,再用两块DAC0800实现幅频特性曲线的显示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)