本方法适用于模拟电路(对数字噪声敏感)和数字电路混合时,尤其是包含高频和大电流电路时。

一、器件布局

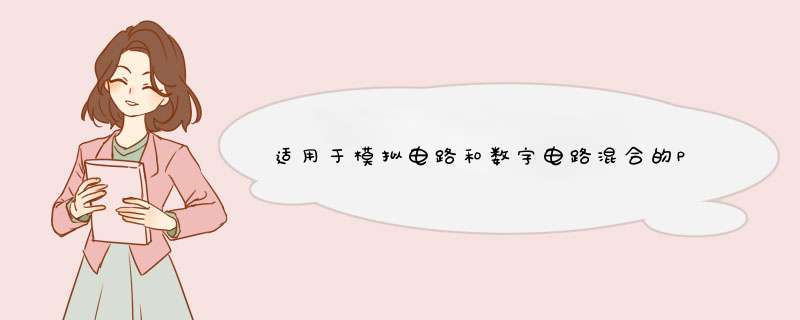

模拟电路应该与数字电路分开,使得它远离开关噪声。

高噪声和高频器件应该布局在靠近连接器/电源。

图 1 推荐的器件布局

二、地的处理

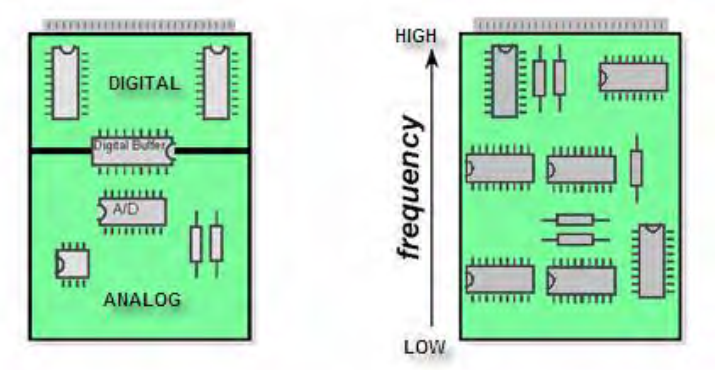

每个部分(模拟和数字)使用独立的地

尽量使用地平面

如果没有地平面,各个地的连接可使用” 星” 形布线

― 尽量提供独立的地电流回路

― 对于小电流/低速信号的器件,回路可以共享(如U1和U2)

― 从头到尾,地线应尽量宽(最窄要达到布线的有效宽度)

― 避免地线环路

― 数字电流不要穿过模拟器件

― 大电流和高速电流不要穿过模拟和低速器件。

― 任何情况下,布线长度尽量短,降低有效电感和电阻

当有地平面时,尽量使用其作为电流回路

为模拟部分提供独立的地平面,模拟地平面和数字地平面分隔开。

避免因顶层的地平面和底层的地平面布线形成环路。

在地平面上,地电流会走最短的路径;如果信号线需要在地平面一边走线,应该尽量短,

且垂直于地电流回路。

即使模拟和数字部分有独立的地,只有一个电气点能作为系统级的参考地,比如两个地应该单点连接;这个点通常作为参考的地。连接最好使用一个磁珠或者电感,可以起到去耦作用

图 2 星形地连接

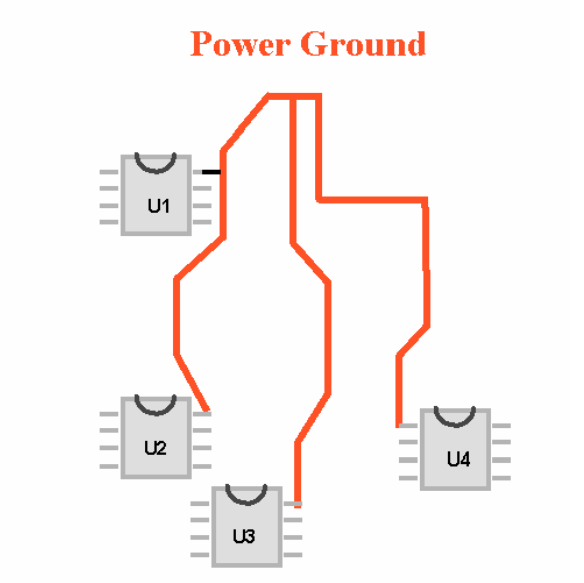

三、旁路和去耦电容

旁路电容给高频电流提供一个低阻抗的通路,降低电源线上的噪声电流。通常, 0.1uF电容可以满足,并应该离器件尽量近。

一个去耦电容将两个电路隔开;这样可以有效的防止噪声从一个电路传到另一个。可以和一个电感一起使用,形成一个低通滤波。这种情况建议使用10uF电容,并应该离电源较近。

图 3 旁路和去耦电容

四、电源层

尽管不如地平面那么重要,当然有电源平面会更好。

对于两层板,电源平面可以用宽的走线来替代(宽度为其他走线的2到3倍)

重要和复杂的设计需要多层板。

这种情况下,建议地和电源平面使用不同的层。

由于很多元件是贴片器件,它们的连接位于电路板的外面一边上(通常是顶层),所以内部层可以被指定为电源和地平面,从而利用层间分布电容。

如果超过4层板, 高速信号可以被保护在地和电源层之间。低速信号放在外层。

五、信号走线 不同部分(模拟和数字)的信号/电源/地不要重叠。否则,重叠部分的分布电容可能把高速的数字噪声耦合到模拟电路。

图 4 信号走线 让数字信号(尤其是高频,高噪I/O或大电流)远离模拟信号。即使走线和平面之间很小的电容也会耦合进足够大的噪声,不仅是基频还有谐波。 高阻抗的电线对电容耦合进来的噪声非常敏感,尤其是来自临近的走线上快速变化的电压(比如数字时钟)。为了减少电容,要增加两条走线间的距离,减少两条走线的长度和厚度。

图 5 走线的推荐距离

为了使寄生电感电容最小,信号线通常来说应该尽量短。

为了使串扰最小,应该尽量避免信号线平行布线。如果不可避免,应扩大平行线间距为信号线宽度的3倍。

使电源和地线之间环路最小(当没有地平面时),避免” 回路天线” 效应。

图 6 推荐的回流路径

通过圆形倒角来使辐射效应最小。

图 7 通过圆形倒角来使辐射效应最小

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)