在宽带隙半导体开关的新时代,器件类型的选择包括SiC MOSFET 和 GaN HEMT 单元,它们都具有自己的特性并声称具有最佳性能。然而,两者都不是理想的开关,因为这两种器件类型在某些领域都有局限性,特别是在它们的栅极驱动要求和“第三象限” *** 作方面。

SiC FET 是另一种选择

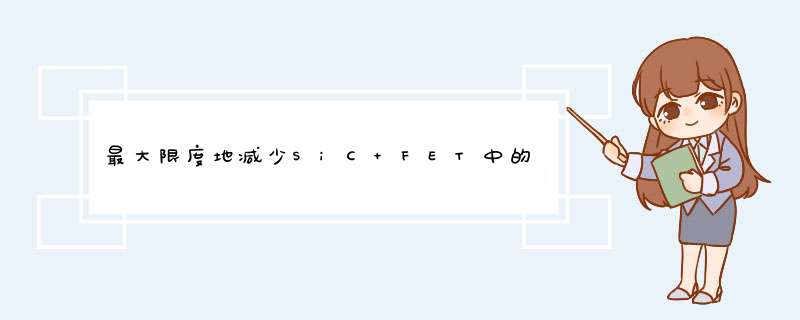

不过,还有另一种选择;UnitedSiC FET 是 SiC JFET 和低压 Si MOSFET 的共源共栅组合,它产生的器件具有 SiC 的所有速度,并利用 SiC 的最低传导损耗优势,但具有简单的栅极驱动和快速、低用于第三象限传导的损耗体二极管(图 1)。

图 1:SiC FET — SiC JFET 和 Si MOSFET 的共源共栅

SiC FET 速度极快,边缘速率为 50 V/ns 或更高,这对于最大限度地减少开关损耗非常有用,但由此产生的 di/dt 可能达到每纳秒数安培。这会通过封装和电路电感产生高电平的电压过冲和随后的振铃。在这些电流变化率下,简单的分析告诉我们,即使是几十纳亨也能产生数百伏的过冲(来自E = – L ( di / dt ))。最小化这种杂散电感对于快速开关 WBG 器件至关重要;然而,这在实际布局中很难实现,这些布局必须在高压组件之间实现安全间隙,并且使用更大的半导体封装以获得更好的热性能。

过冲风险超过设备的额定电压并增加组件的长期应力,但快速边缘也会引起绝缘击穿并倾向于产生更多的 EMI,需要更大、更昂贵和更高损耗的滤波器。因此,实际电路通常故意降低这些类型的快速开关的边缘速率,允许使用具有更好传导损耗和更小的滤波器的低压器件,从而抵消略高的开关损耗。

减慢开关边沿可减少过冲和 EMI

有两种常见的方法可以减慢开关边沿:增加栅极电阻和在器件的漏源极端子上使用缓冲器。

增加栅极电阻确实会降低 dV/dt,从而减少过冲,但对随后的漏极电压振铃几乎没有影响。栅极电阻的减速效应取决于器件的总栅极电荷,而后者又取决于诸如栅极-源极电容和“米勒”效应等参数,该效应表现为随着器件切换而变化的栅极-漏极电容。开启和关闭延迟可以通过使用两个带二极管控制的栅极电阻器单独控制,但整体效果很难在所有工作条件下优化条件。此外,增加栅极电阻会导致栅极驱动波形延迟,这在高频下可能会出现问题。

相比之下,简单的 Rs-Cs 缓冲器可以通过有效地向开关的漏极增加电容来降低 dV/dt。另一个效果是电压上升和关断时电流下降之间的重叠减少了,因为一些电流被转移到充电 Cs 中,从而降低了器件的开关损耗。当开关打开时,电容器放电电流必须受到限制,因此串联添加一个电阻器,它还可以在设备关闭时抑制振铃。缺点是电阻在此过程中不可避免地会耗散一些功率,并且在一定程度上抵消了半导体中开关效率的增益。

缓冲器可以是低损耗解决方案

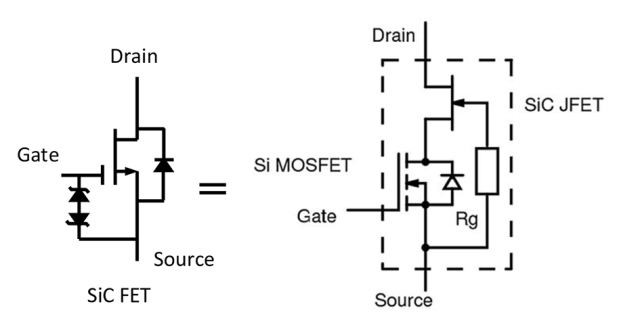

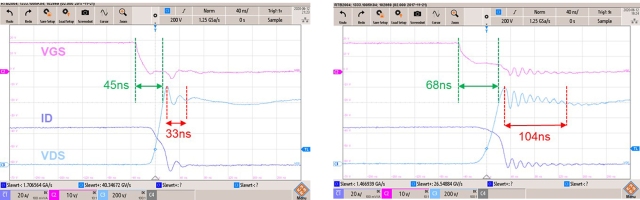

UnitedSiC是 SiC FET 技术的领导者,其所做的工作表明,与增加栅极电阻相比,只需要一个带有相应低功率电阻的非常小的缓冲电容器即可实现对 dV/dt、过冲和振铃的更有效控制独自的。当小型器件缓冲器与随后可以使用的较低 Rg 结合使用时,结果是整体损耗更低,波形更清晰。这种方法适用于 UnitedSiC 的 FET 和传统的 SiC MOSFET。图 2 中比较了具有 200 pF/10 Ω 缓冲器的器件(左)和添加了 5 Ω 栅极电阻器的器件(右)之间的振铃和 dV/dt。虽然两种方法都类似地调整到相同的 V DS 在关断期间达到峰值,缓冲器版本清楚地显示出更短的延迟时间和更好的振铃阻尼。

Figure 2: Using an RC device snubber reduces dV/dt, ID/VDS overlap, and ringing in SiC MOSFETs. (ID = 50 A, V = 800 V, TO247-4L; left, SiC MOSFET turnoff waveform, Rg,off = 0 Ω, Rs = 10 Ω, Cs = 200 pF; right, SiC MOSFET turnoff waveforms, Rg,off = 5 Ω, no device snubber)

总损耗是传导损耗、上升沿和下降沿上的器件开关损耗以及缓冲电阻器中耗散的任何功率的组合。与 SiC MOSFET 器件进行比较,UnitedSiC 的测试表明,在高漏极电流下,使用缓冲器解决方案的关断能量损失 (EOFF) 可能是仅使用栅极电阻等效调谐峰值电压时损失的 50%。同时,开启能量 (EON) 略高(仅约 10%),因此,例如,对于在 40 kHz 和 48 A/800 V 下开关的 40-mΩ 器件,净效应是总收益每个周期约 275 µJ 或 11 W 的缓冲器。此比较在图 3 中显示为蓝色和黄色曲线。黑色曲线是具有缓冲器和优化栅极开关电阻器的 40-mΩ UnitedSiC SiC FET 器件的性能,

图 3:比较带和不带缓冲器的 SiC 开关的总开关损耗

缓冲电容器在每个开关周期完全充电和放电,但重要的是要注意,这些存储的能量并未全部耗散在电阻器中。事实上,大部分 CV 2能量实际上是在器件开启期间耗散的。在引用的示例中,在 40 kHz、ID 40 A、VDS 800 V 和 220-pF/10-Ω 缓冲器时,总耗散功率约为 5 W,但电阻中仅约 0.8 W;其余的在开关中。这允许在适当的额定电压下使用物理上小的电阻器(甚至表面贴装)。

UnitedSiC 提供采用 D2pk7L 和 DFN8×8 封装以及 TO247-4L 封装的器件,以获得最佳热性能。TO247-4L 部件与源极采用开尔文连接,有效地消除了源极电感的影响,改善了开关损耗,并在高漏极 di/dt 下产生了更清晰的栅极波形。

结论

器件缓冲似乎是管理开关过冲、振铃和损耗的“蛮力”解决方案,对于较旧的技术(如 IGBT)来说,肯定就是这种情况,因为它们的“尾电流”很长,需要大型且有损的缓冲网络。然而,宽带隙器件,尤其是 SiC FET,可以使用该技术作为栅极电阻调谐的卓越替代方案,以提供更低的整体损耗,并且可以使用紧凑、廉价的组件来实现。

审核编辑:刘清

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)