到2030 年之际,晶体管密度将增加10 倍,这将使得英特尔在芯片上发展到拥有1 万亿个晶体管。

编译来源:electronicdesign

英特尔首席执行官 Pat Gelsinger 表示,未来几年推动摩尔定律的不仅仅是更小、更便宜的晶体管。

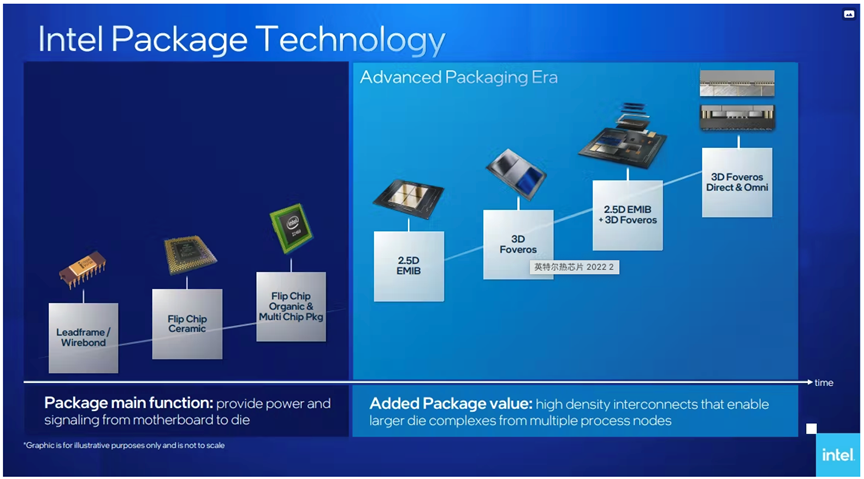

半导体行业正在进入一个新时代,曾经按照摩尔定律试图将所有东西都安装在单个片上系统 (SoC) 上,但现在英特尔将把重点放在能在封装系统(SiP)中压缩什么。

Gelsinger说,从用于数据中心的未来旗舰 Sapphire Rapids Xeon 可扩展 CPU 到 Meteor Lake 的新个人计算机芯片系列,所有产品都在采用 2.5D 和 3D TIle-based 芯片设计以提高性能。

因为在制造最先进芯片中落后,希望回到巅峰的英特尔正在形成新的理念。多年来,英特尔的斗争首次动摇了其市场主导地位。Gelsinger 正试图在相当长的一段时间内执行该公司最雄心勃勃的路线图之一,以超越台积电和其他领先的竞争对手。

他还在建立一家名为 IntelFoundry Services 的公司,与台积电展开竞争。英特尔根据其他人的设计合同制造芯片,同时依靠竞争对手的代工厂来制造更多自己的产品。

晶圆厂的概念比以往任何时候都更加复杂。代工厂现在不仅要生产晶圆,还要生产与软件连接在一起的整个系统。

Gelsinger 说,“如果你仔细想想,机架正在变成一个系统,而且这个系统正在变成一个由多个裸片和Chiplet组成的先进封装。这个系统正在成为未来的先进封装技术。”

英特尔作为“系统代工”的角色是帮助扩展围绕Chiplet和2.5D和3D高级封装技术的生态系统,为创新的定制芯片和系统级集成创造新的可能性。

从芯片到封装

这些言论表明,即使制造芯片变得更加昂贵且技术上具有挑战性,英特尔的 CEO 并不相信摩尔定律即将消亡。Gelsinger 说:“摩尔定律——随着尺寸随着时间的推移而不断缩小的晶体管能力持续翻倍——是我们能够完成的一切的根本驱动力。”

这为英特尔提供了新的方法来制造更便宜的芯片,更适应客户的软件,并能够满足在半导体上运行的一切对更多计算、连接和人工智能的需求。

虽然英特尔今天可以在一个封装中压缩超过1000 亿个晶体管,但他表示,英特尔正在开发工艺和封装技术,这将使其在本世纪末达到 1 万亿个。

他列举了晶体管设计方面的创新,包括即将推出的称为 RibbonFET 的环栅 (GAA) 晶体管和新的 Power Via 背面功率传输系统,以及后来使用的极紫外 (EUV) 技术和高 NA EUV 。他说,这些是未来几年制造更小、更快、更节能晶体管的关键。

但晶体管设计的创新只能走到这一步。英特尔还在利用其广泛的 2.5D 封装,包括嵌入式多芯片接口桥 (EMIB) 及其 3D 逻辑堆叠技术,以帮助将更多的硅芯片以及晶体管连接到高密度芯片封装中.

一个例子是英特尔为美国 Aurora 超级计算机构建的高性能 GPU。该处理器由近 50 个有源硅片组成,并结合了英特尔的 2.5D 和 3D 封装。

封装中的每个TIle,将3100平方毫米的硅封装成2330平方毫米,使用英特尔和台积电的不同技术节点制成,转化为1000多亿个晶体管。Gelsinger 指出,“今天的系统问题将成为明天的Chiplet问题。”

新的理念

英特尔希望做的是给客户同样的能力来拆卸可能受芯片面积、成本或功率限制的芯片,然后将Chiplet重新组装成一个封装。

英特尔称之为Chiplet或TIle背后的概念是分而治之。这些微小的硅方块是从以前的单片硅片中切下来的。然后,将Chiplet重新组装到一个封装中,该封装比其各部分的总和还要大。除了节省空间外,这让设计人员可以自由地将各种各样的Chiplet粘在一起,就像在非常小的电路板上组装零件一样。

英特尔领先服务器处理器中的单片芯片还存在其他弱点。它们有更多的空间来容纳影响产量的缺陷,这使得它们在较小节点的每个晶体管上更加昂贵。

Gelsinger还指出,封装中的所有不同TIle都可以使用最适合不同功能的任何工艺节点单独制造:电源、射频、模拟、高级逻辑。

这样,最先进的处理技术可以在主计算块中使用。与设计新的IP块相比,在传统节点上构建非关键块,甚至重用现有芯片中的block,可以节省资源。他将这种方法称为“针对正确的问题使用正确的晶体管”。

“但我们还需要以一种非常易于使用的可组合方式将它们联系在一起,为设计人员提供抽象概念,使他们无需在芯片级了解每个执行和硬化 IP 的细节,就能够完成更复杂的事情。”

Gelsinger 正在建立向所有人开放的英特尔代工业务。除了软件之外,英特尔还让其客户可以从其内部存储库和外部公司访问IP库。他说,英特尔愿意推出基于指令集架构(ISA)的芯片,从x86、Arm到RISC-V。英特尔还将使用代工产品(例如其 Chiplet Studio 技术套件)来帮助 Chiplet 生态系统成熟。

所有这一切的关键将是创建一个标准接口,允许一切无缝地结合在一起。

为此,英特尔一直是新兴的UCIe 接口背后的推动力之一,该接口是一种建立在 PCIe 总线之上的开放的、行业标准的芯片到芯片互连。

让 UCIe 标准脱颖而出的原因在于,许多世界顶级半导体公司都在支持它,AMD、Arm、Marvell、NVIDIA 和高通,以及三星和台积电的代工厂。

支持 UCIe 的还有云和技术领导者 Google、Meta 和 Microsoft。总共约有 50 家公司加入了 UCIe 联盟,以帮助构建Chiplet生态系统,为不同供应商在封装中采用不同工艺技术设计和制造的 IP 的混合和匹配打开了大门。

“现在我们正在采用一个芯片上的单片系统,该系统可能在芯片尺寸、成本和功率方面受到限制,并能够将其分解到一个解决方案中,该解决方案不仅利用了先进的封装,还利用了开放式UCIe标准能够实现的所有标准混合和匹配功能。”Gelsinger 说。

随着越来越多的公司采用 2.5D 和 3D 芯片设计,像 UCIe 这样的即插即用接口也应该有助于通过规模经济和易于集成来降低成本,使该方法更易于使用。

他说:“你可能会说,'我从英特尔获得一个Chiplet,我从台积电工厂获得一个Chiplet,也许电源组件来自 TI,也许 I/O 组件来自GlobalFoundries。英特尔拥有最好的封装技术,因此他们会将所有这些Chiplet组装到市场上。”

Gelsinger 补充说:“我们确实看到了这种混合和匹配。当我说机架正在成为一个系统时,系统正在成为一种基于封装的高级小芯片,这正是我们的意思。”

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)