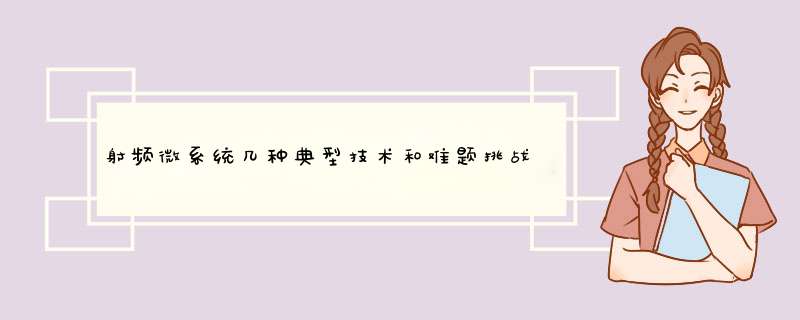

传统的封装技术已难以满足飞速发展的电子信息系统的高密度集成需求,随着先进封装技术的发展,射频微系统成为小型化电子产品的重要组成部分,可以在微纳尺度下实现高性能电子系统,为电子信息设备多方面的技术变革提供了重要技术路径[1],典型射频微系统如图1所示。自射频微系统技术问世以来,美国、日本等发达国家就将其列为现代前沿核心技术,并相继实施了“超越微缩(Beyond Scaling)”、“电子复兴ERI计划(Electronic Renaissance IniTIaTIve)”、“E-CUBES计划”等项目计划。另外,台积电、Intel、IBM等公司也纷纷对射频微系统的新技术、新工艺展开研究并取得不菲成果。掌握射频微系统技术对于国家实现核心技术自主可控具有重要意义,因此,我国近年来对射频微系统技术高度重视并进行深入研究[2],先后大力支持了遥感信息处理微系统集成、d载多模通信等方向的课题研究工作。

本文首先对射频微系统的发展与应用进行分析,接着梳理总结了射频微系统几种典型技术的内涵及研究现状,最后针对国内射频微系统的发展现状,探讨了现阶段主要存在的问题,并对射频微系统未来发展策略提出了一些建议。

1 射频微系统技术概述

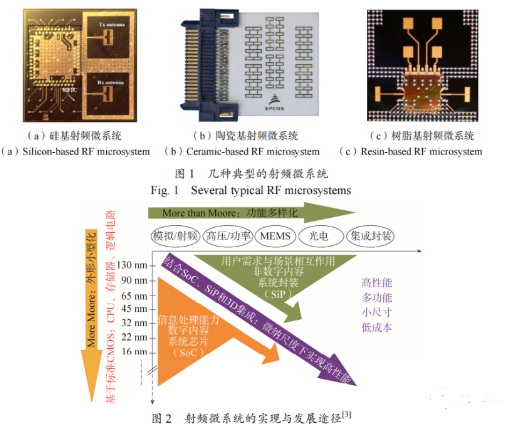

摩尔定律已经逼近极限,目前集成电路主要沿三个方向发展:延续摩尔定律(More Moore)、拓展摩尔定律(Morethan Moore)以及超越CMOS(Beyond CMOS)。而射频微系统技术融合了三维异质异构集成、微纳工艺等技术,可将延续摩尔定律和拓展摩尔定律的技术优势结合起来,实现高性能、多功能、小尺寸、低成本的电子封装。射频微系统的实现与发展途径如图2所示。

1.1 射频微系统技术在军民领域的应用

射频微系统主要针对雷达、通信、电子对抗、物联网等产品的低成本、小型化、多功能化等需求,在航空航天、船舶、武器等军事领域,以及5G移动通信、WiFi、生物医疗、工业控制、汽车电子等民用领域都有着巨大的生命力。

在军事领域,射频微系统作为支撑航天工程和武器装备战略发展的核心技术之一,能够在大幅减小武器系统的体积与功耗的同时兼顾多功能集成和智能化,从而增强武器装备在作战时的机动性、可靠性和隐蔽性[4]。美国、德国、日本等发达国家已取得较多成果,研制出了采用射频微系统技术的新一代雷达、通信、电子战等先进武器装备。2013年,美国NASA成功发射的4颗采用微系统技术开发的手机卫星尺寸与马克杯大小相当,可以满足多种系统需求[5]。2015年9月,日本电报与电话公司(NTT)、富士通和美国NIST研究所采用微纳制造工艺,将聚酰亚胺作为印制电路板,结合太赫兹高灵敏放大器芯片集成技术,合作研发出世界首个内置天线的紧凑型300GHz接收器,体积仅为0.75cm3。2016年4月,德国Fraunhofer研究所采用InGaAs器件技术和特制印刷电路板研发出了一款高频微系统模块,体积仅为78mm×42mm×28mm,可使雷达模块体积缩减至烟盒大小。2018年,美国DARPA与佐治亚理工学院等机构合作启动了三维单芯片系统3DSoC(3DSystemonChip)项目,实现了存储、逻辑和收发组件等单元小型化、一体化、高性能三维射频微系统封装芯片,并于2020年6月的“2020 VLSI技术与电路研讨会”上首次对单片集成3D SoC技术与SRAM和RISC-V计算核进行了硬件演示,并宣称已为3D SoC技术平台开发了工业级代工工艺设计套件PDK(Process Design Kit)。

在民用领域,射频微系统已经广泛应用于短距离无线通信、物联网、5G通信、智能驾驶等领域。通过TSV技术、晶圆键合技术等先进射频微加工技术,可以大大提高微波收发组件、数据处理器件、高频存储器件、高效电源等的集成度,优化产品性能。2015年,英特尔公司[6]通过将收发组件集成于包含天线元件的液晶聚合物LCP(Liquid Crystal Polymer)封装中,实现了一款集成了18个收发组件的60GHz相控阵射频微系统,主要用于60GHzWiGig领域,封装薄至0.41mm。2017年,IBM公司为毫米波5G通信系统开发了一款基于高密度互连HDI(High Density Interconnector)工艺的Ka频段16通道相控阵射频微系统[7],尺寸仅为6.85mm×6.85mm×1.61mm。2020年,新加坡A*STAR研究所针对5G应用设计了一款封装尺寸为10mm×10mm×0.8mm的双层模压扇出式晶圆级封装FOWLP(Fan-out Wafer Level Packaging)射频微系统[8],散热能力高达5W。2020年,大陆集团宣布,通过赛灵思公司的Zynq®UltraScale+™MPSoC平台,开发出了新型高分辨率远程4D成像雷达传感器ARS540,可在智能驾驶中实现复杂驾驶场景的多目标跟踪、快速识别相应道路潜在的危险物体等功能。

1.2 射频微系统典型技术

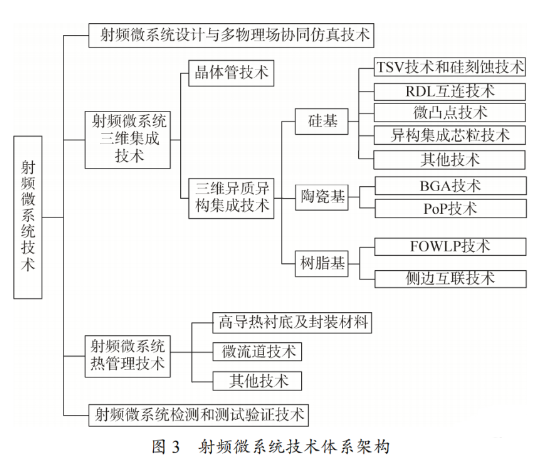

射频微系统典型技术主要包括射频微系统设计与仿真、射频微系统三维集成技术、热管理技术以及检测和测试验证技术。射频微系统技术体系架构细分图如图3所示。

2 射频微系统设计与多物理场协同仿真技术

射频微系统设计主要是根据微系统的应用需求对各功能模块进行合理设计及布局,以实现三维射频微系统封装中电路信号的完整性要求,避免信号串扰问题和垂直互连结构信号过渡不连续问题。

在射频微系统技术实现的产品工作过程中,电、磁、热、力等物理场并不是单独存在和作用的,各物理场间往往会相互耦合、相互影响[9],因此,在射频微系统封装的设计中需要进行多物理场协同仿真研究。通过对射频微系统中光、机、电、磁、热、流体、应力应变等多维度物理场在微小尺度下的耦合与互扰进行研究,以解决多元参量间相互约束和平衡问题,进而采用一些特殊的设计来提高射频多芯片的电气性能,并减少多物理场对产品可靠性的影响。2016年,美国伊利诺伊大学香槟分校针对集成微流道冷却的三维射频微系统,提出了一种包括全波电磁、流体、瞬态共轭热交换的多物理场协同仿真技术[10],其通过对流体流动的控制方程与温度解耦解析出流体的速度场,全波电磁和瞬态共轭传热分析通过温控材料来进行耦合迭代分析,实现了精确、高效的多物理场协同仿真,并验证了微流道散热的有效性以及对3D射频微系统高频特性的热影响。

3 射频微系统三维集成技术

结合延续摩尔定律与拓展摩尔定律的射频微系统三维集成技术,可以分为晶体管技术、高密度封装功能基板制造技术、三维异质异构集成技术。其中,晶体管技术主要在延续摩尔定律方面进行技术研究和突破,以获得按比例微缩的高性能芯片;三维异质异构集成技术主要用于拓展摩尔定律,通过先进封装技术,在成本相对低廉的情况下实现系统小型化、多功能和高性能。

3.1 晶体管技术

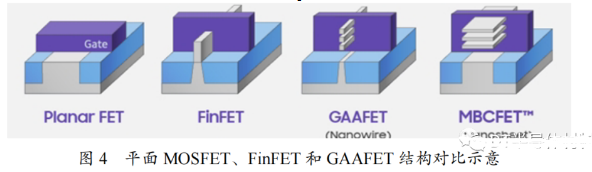

随着摩尔定律的发展,传统平面MOSFET结构的限制使得半导体工艺逐渐难以满足“等比例微缩”的尺寸发展需求。为继续向微型化发展,一种新结构——三维结构的鳍式晶体管FinFET(FinField-EffectTransistor)——应运而生。英特尔、三星、台积电陆续在其工艺制程节点上推出了各自的FinFET技术。FinFET技术最主要的特点是栅极(Gate)三面环绕源极(Source)和漏极(Drain)之间的沟道,由于增加了栅极对沟道的控制面积,因此能有效减小漏电流,增强沟道控制能力,进一步缩短栅极长度,减小晶体管面积。

为应对芯片采用FinFET技术微缩到7nm后的瓶颈,三星、英特尔等突破性地提出了环绕栅极场效应晶体管GAAFET(GateAllAroundFieldEffectTransistors)技术。GAAFET技术在给定的区域内封装了更多的高性能晶体管,其与FinFET技术相比,减小了标准单元的宽度。GAAFET技术可以分为两种,一是常规GAAFET,使用三层纳米线(nanowire)替代FinFET的鳍;二是多桥通道场效应晶体管MBCFET(MulTI-Bridge-ChannelMOSFET),其使用更厚更宽的纳米片(nanosheet)作为晶体管的鳍,增加了沟道和栅极间接触面积,从而增大了电流通过量[11,12]。各结构对比如图4所示。

3.2 三维异质异构集成技术

射频微系统采用三维异质异构集成技术,可将不同工艺、材料甚至生产厂家的芯片或功能模块立体集成在同一封装内,实现产品小型化、高集成和多功能的目标。其中,常用的高密度封装基板主要有硅基板、陶瓷基板以及树脂基板等。

3.2.1 硅基

硅基射频微系统在三维集成时通常采用硅通孔TSV(ThroughSiliconVia)、再布线RDL(RedistribuTIonLayer)等工艺技术实现多层硅片垂直互连,并且采用硅刻蚀技术将芯片内埋入基板内达到进一步缩减体积的目的。

3.2.1.1 TSV技术及硅刻蚀技术TSV技术是2.5D/3D集成的关键技术,TSV硅基板表面互连线以及内部硅通孔可实现三维异质异构集成、缩短元器件间距,进而提高电路集成密度,实现射频微系统的小型化和低功耗。TSV技术大概思路是在硅晶圆上刻蚀出通孔后,向孔内填充铜等导体材料,以建立硅片上下表面信号互连通道。其工艺主要实现步骤包括:通孔刻蚀、绝缘层铺垫(防止产生漏电流,材料通常为SiO2)、通孔填充、圆片减薄以及晶片堆叠与键合[13]。

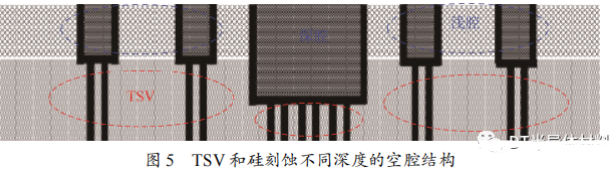

硅刻蚀技术可依据要嵌入的芯片厚度并采用干法刻蚀工艺或湿法刻蚀工艺在硅基板上刻蚀出不同深度的空腔,从而将芯片埋入硅基板内部,减薄厚度,进而提高系统集成度。目前,已有不同深度空腔的一次性刻蚀工艺,即先用湿法刻蚀工艺做出深腔的开窗,然后用干法刻蚀一次性将深腔和浅腔刻出,工艺流程简单。结构如图5所示。

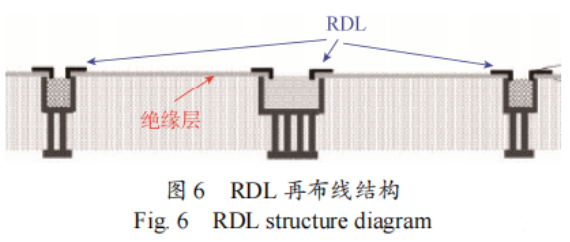

3.2.1.2RDL互连技术再布线RDL技术是通过晶圆级金属布线制程和凸块制程改变原设计的芯片线路接点,使集成芯片适用于不同的封装形式。硅基板RDL大致流程为:先在硅基板上涂覆绝缘层,曝光显影再电镀新的金属导线路径以连接原有接点和新的凸块,进而重新分布接点,实现高密度、高精度布线要求。工艺通常有两种:大马士革工艺和聚合物RDL工艺。如图6所示,内埋芯片可用RDL互连线引出信号到基板表面,结合FAN-OUT扇出工艺,能有效应对引脚较多的芯片。同时,RDL优势还包括:互连线高度较低,上盖板不需要刻蚀深腔;相对于引线键合,其可承受更持久的高温和更高强度的振动冲击,增加了元件的可靠性且能取代部分系统设计,减少设计时间等。

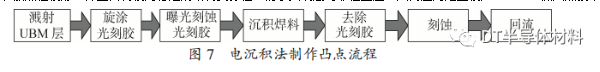

3.2.1.3 微凸点技术硅基射频微系统在进行三维叠层时,常用技术主要有微凸点技术、高分子粘接、Au-Sn共晶焊接等[14],其中微凸点互连技术采用合金焊料和金属,电气互连和散热性较好,并且具有较为稳定的结构支撑性,易于实现高可靠性互连,因而应用范围较广[15]。微凸点技术由IBM公司在20世纪70年代提出,由于其优良特性,直到今天仍备受微系统封装设计人员的青睐。目前,微凸点的制备方法主要有电沉积法、焊料溅射法、模板印刷焊料法等。其中,电沉积法制作凸点流程[16]如图7所示。

3.2.1.4 异构集成芯粒技术异构集成芯粒(chiplet)技术起源于多芯片模块,由AMD公司在上世纪70年代为降低半导体芯片的设计成本而提出。芯粒是可以集成到低延迟中介层上的裸片,不同的裸片可以使用不同的工艺节点制造,甚至可由不同的供应商提供。芯粒设计类似于SoC但价格低于完全集成的SoC设备,其突破了传统的在单个硅片上实现所有功能的限制,采用模块化方法,通过多个被单独制造的不同功能的芯粒来构建硅系统,从而减少设计时间和成本[17]。2017年8月,DARPA启动通用异构集成和IP复用策略(CHIPS)项目,通过添加较小的专用芯粒来设计射频微系统。CHIPS项目的创新之处在于不使用传统印刷电路板而是用硅中介层(interposer)来连接芯粒,芯粒间通过die-to-die技术进行内部互联,从而实现间距更精细的互连集成。

3.2.1.5其他技术Co-EMIB技术是英特尔在公司已有的嵌入式多核心互连桥接EMIB(Embedded Multi-DieInterconnect Bridge)和FOVEROS基础上的进一步创新,在2019年7月的SEMICONWest会议上被提出。其结合了EMIB和FOVEROS3D封装技术的优势,将多个FOVEROS元件互连为一整个封装,可以实现其高I/O密度、高带宽、低功耗、多功能集成。

除以上举例的几种硅基射频微系统异质异构集成技术外,还有许多先进技术,如台积电将小外形集成电路封装SoIC(Systemon Integrated Chips)、集成扇出型封装InFO(Integrated Fan Out)、晶圆级封装CoWoS(Chip-on-Wafer-on-Substrate)等3DIC平台整合在一起推出的3D Fabric先进封装技术;欧洲e-CUBES项目[18]基于TSV技术和空心通孔及金钉凸点键合技术,通过晶圆级封装可实现嵌入式器件的芯片堆叠3D-WLP(Wafer Level Packaging)和器件级别的三维射频微系统3DSoC、可压缩微互连CMIs技术[19]等等。更多先进异质异构集成技术还在不断地涌现发展,硅基射频微系统在未来有着巨大的潜力。

3.2.2 陶瓷基

射频微系统的陶瓷基板采用共烧陶瓷技术制备。由于烧结温度不同,共烧陶瓷[20]主要分为高温/低温共烧陶瓷HTCC/LTCC(High-Temperature Co-fired Ceramic/Low-Temperature Co-fired Ceramic),HTCC多层基板具备更高的机械强度和散热系数,化学性能也更为稳定,而LTCC基板一般电性能较好、并且可内埋无源元件,但机械强度和导热率较低。陶瓷基射频微系统多采用球栅阵列BGA(Ball Grid Array Package)技术和叠层封装技术实现立体封装。

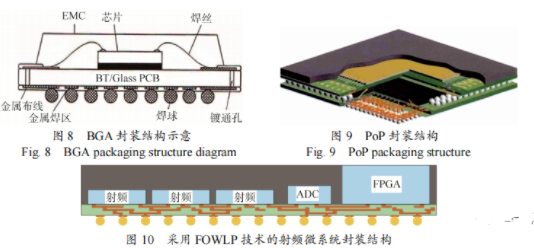

3.2.2.1 BGA技术BGA技术常用于多引脚小尺寸电子产品的封装。BGA封装结构如图8所示,其可在封装基板背面以面阵列形式排列的焊球代替传统键合金丝和连接器,用于与外部电路互连并传递射频信号[20],与传统表面贴装SMT(Surface Mounted Technology)封装相比,具有装配简单、成本低,布线难度小、互连距离短、尺寸小、焊球可自动对齐等优点。根据基板材料的不同,可以将BGA封装分为塑封球栅阵列PBGA(Plastic Ball Grid Array)、载带自动键合球栅阵列TBGA(Tape Ball Grid Array)和陶瓷球栅阵列CBGA(Ceramics Ball Grid Array)。其中,CBGA封装基板材料一般为共烧陶瓷基板。BGA技术近年来广受CPU等高密度、高性能、多引脚IC和射频微系统封装设计者的青睐,如英特尔Pentium大功率高集成度CPU芯片采用了CBGA封装,并在外壳安装微型风冷装置,以提高电路性能与可靠性。

3.2.2.2 PoP技术叠层封装PoP(PackageonPackage)技术在2007年随iPhone一起进入公众视野。PoP封装结构如图9所示[21],其可将先单独封装制造的逻辑、存储和射频等模块再垂直堆叠互连集成为一个封装整体,芯片封装类型更加灵活,在硅基、陶瓷基、树脂基的射频微系统集成中都有应用。如2020年6月,在第70届IEEE电子元件与技术会议ECTC(ElectronicComponentsandTechnologyConference)上,印度微系统研究人员[22]基于PoP技术和LTCC工艺设计了一款用于5G毫米波通信应用的收发射频微系统封装,同时,新加坡A*STAR研究所[23]研究人员也对采用扇出型晶圆级封装FOWLP方法的PoP射频微系统封装展示了一些新的研究发现。

3.2.3 树脂基

3.2.3.1 FOWLP技术树脂基射频微系统通常采用扇出型晶圆级封装FOWLP方法,通过晶圆重构将多个射频芯片和数字芯片粘贴为同一区域,然后进行多层再布线并制备凸点,最后进行切割分离,得到能够与主板射频互连的一体化微系统封装[24]。图10是一种典型的扇出型晶圆级微系统封装结构,相比于传统的以引线键合技术为基础的封装,其在成本、尺寸、性能方面都有突出优势,并可以实现不同功能材料芯片的系统级异质异构集成。各代工厂都有其独特的FOWLP方案,如英飞凌的嵌入式晶圆级球栅阵列eWLB(EmbeddedWaferLevelBGA)技术,TSMC的In FOFO WLP技术,三星的FOPLP技术等。

3.2.3.2 侧边互联技术

基于树脂封装的三维射频微系统,通常先通过层叠的方式对单层微波电路进行立体组装,然后使用树脂填充封装,树脂封装脱模后对封装表面金属化并刻蚀布线,不同层间的射频垂直互联通过采用侧边互联技术以每层射频电路端面与侧边表面类共面波导CPW(Co-PlanarWaveguide)结构的形式实现。图11展示了一个树脂包封的三维多芯片射频组件微系统[25]。

射频微系统最终目的是要满足产品微小型化、多功能化、低成本化的发展趋势与要求,晶体管技术、三维异质异构集成技术正是服务于这一目的而诞生和发展的。先进的集成工艺技术带来可以满足民用领域和军事领域应用需求的优异产品,而科技进步带来的对微系统集成度和性能更高的要求也在推动着射频微系统集成技术的不断进步,继而攀向一个又一个高峰。

4 射频微系统热管理技术

“小”是电子产品永恒的追求。随着微系统集成度和小型化程度的不断提高,微系统封装内热流密度大等问题逐渐变得不容忽视。传统热传导、强迫液冷、风冷等热管理技术存在着占用空间大、不易集成、散热效率低等缺点,已经难以满足高集成度射频微系统的散热需求,在保证封装结构紧凑的前提下如何进行高效散热已成为国内外团队的研究重点之一[26,27],现阶段射频微系统常用的热管理技术有使用高导热材料衬底和封装以及微流道技术等。

4.1高导热材料衬底及封装基于高导热材料衬底及封装进行散热的方式设计简单可靠,但对材料的热导率以及与硅、砷化镓等材料的热匹配性等性能要求较高,目前较为常用的高热导率衬底有多层石墨烯、金刚石、碳化硅等,高热导率热沉及封装材料有金刚石基(铜、铝、银)、石墨复合材料等。

DARPA于2011年启动近结热传输NJTT(Near-JunctionThermalTransfer)项目[28],目的是通过功率器件的局部热管理,降低半导体器件热阻抗,其中一项重要内容即为高导热金刚石衬底。多个研究团队参与研究并取得了一定进展[29],如雷神公司采用金刚石衬底实现了GaN器件1/5至1/3的热阻降低;BAE系统公司将金刚石与薄GaN键合以减小热膨胀系数CTE(Coefficient of Thermal Expansion)不匹配影响;诺格公司在碳化硅衬底上刻蚀金刚石过孔提高了芯片散热效果。这方面国内起步较晚,目前,中电55所已完成了76.2mm多晶金刚石衬底GaNHEMT的转移键合[30]。

国外对高热导率封装材料与热沉研究较早并较为成熟,如金刚石、石墨复合材料已经广泛用于微电子封装热沉。美国劳伦斯利弗莫尔国家实验室在1995年就开发出了一种热导率可达600W/(m·K)、CTE与硅相近的金刚石-铜复合材料,并已应用于多芯片模块的热管理设计;国内北京研究总院和北科大[31]在2009年制备的金刚石-铜复合材料的热导率可达503W/(m·K)。石墨复合材料的代表性散热产品有美国爱美达公司的K-core、珉泰克公司的PYROID热解石墨等。

4.2微流道技术微流道技术由斯坦福大学的Tuckerman和Pease在1981年提出,并随着微系统加工工艺的发展而逐渐成熟。相比于传统散热方式,微流道技术可将散热性能提升几个量级,并且更加易于集成、占用体积更小。2006年,IBM公司在风冷基础上开发出高热导界面技术,通过制作的芯片表面树状结构将散热效率提升数倍;之后,苏黎世实验室提出喷射冲击冷却后再通过树状结构迅速回收液体的水冷散热方案,将散热效率提升至原先的6倍左右[32];2007年,上海交通大学联合国家重点研究室设计出了一种新型变截面微流道散热器,可输送5×107W/m2的热通量[33];2012年,DARPA启动芯片内/芯片间增强冷却ICECool(Inter-Chip Enhancement Cool)项目[34],目标是探索先进的热管理技术,其中,嵌入蒸发微流道冷却技术被最为看好以解决远端冷却局限;2017年,普渡大学在芯片间设置分级微孔集分水腔和高长宽比微流道阵列等,微流道散热效率提升10倍;2018年,欧洲微电子研究中心IMEC(Interuniversity Microelectronics Centre)展示了其3D打印的微流道芯片换热器,可将热流密度达100W/cm2的芯片温升控制在15℃以下。

4.3 其他技术除上述技术外,射频微系统热管理技术还在不断推陈出新。如2015年Kim等[35]人采用热电薄膜制冷技术设计了一种新型散热器;2018年,中电26所提出了一种基于微冷控制元件的主动微系统冷却技术[28],可通过压电驱动为内部微流道液冷循环提供足够的压力与工作流量,进而有效散热。

5 射频微系统检测和测试验证技术

射频微系统检测和测试验证主要包括以下内容:

①微制造工艺的检测,如TSV结构的漏电流测试、微纳结构的击穿电压测试、微凸点形貌测试等微缺陷检测排查;②射频微系统的电学性能检测,如频率、发射功率、接收/发射增益、噪声等参数的目标符合性验证;③射频微系统的可靠性验证,如TSV/TGV转接板、晶圆键合、材料外延的评估,射频微系统模块力学、热学可靠性测试与寿命预测等。

目前,国内外多家机构在射频微系统测试技术方面都开展了一定研究。日本ASET在2008到2012的5年间,发展了关于设计环境、芯片测试等技术,以支持日本梦芯工程项目;我国台湾地区先进堆叠系统与应用研发联盟Ad-STAC,整合各种3DIC设计、技术、设备、材料、封装与测试开展研究,以达到推动台湾3DIC设备及材料自产化的目的[36];长电科技、通富微电、天水华天等企业均对系统级封装测试方向进行了多年研发,在模型电参数提取等方面已积累了一定经验;在我国“02”专项、“973”计划等的支持下,中科院微电子所与多家研究机构联合,对射频微系统三维封装设计、TSV测试方法、混合信号芯片测试技术等关键技术开展了多项研究并获得了一定成果[37,38]。

6 射频微系统发展策略分析

国外的射频微系统技术起步较早,美国、欧洲、日本等发达国家早在上世纪末已将微系统技术列为先进核心技术,近十年来已通过多个工程项目落地了射频微系统在设计仿真、三维集成、散热、封装测试等方面的各项技术开发和应用成果。目前,各机构仍然在持续探索射频微系统的新材料、新工艺、新技术。

6.1我国射频微系统技术发展现状近年来,我国对射频微系统技术高度重视。2011年3月,我国完全自主研发的数字处理器芯片“魂芯一号”问世,打破了国外高端数字处理芯片对我国的垄断;2012年,航天科技集团公司元器件保证研究中心组织系统开展了航天未来片上集成系统论证工作,为航天微系统的发展发挥了重要作用;2014年,国务院颁布的《国家集成电路产业发展推进纲要》中明确指出,到2015年要达到中国厂商占30%左右先进封装收入的目标;国发(2015)28号《中国制造2025》与国发(2016)43号《“十三五”国家科技创新规划》将微系统技术作为提升新一代信息技术产业自主发展的重要能力,与新一代信息技术重点进行发展。目前,我国在需求牵引和技术推动下,已先后支持了机载综合处理、遥感信息处理、d载多模通信等方向的军用微系统集成课题研究工作,并取得一定成果和进展,已初步建成了SoC、SiP微系统技术平台和共享IP库,目标是统筹国内研究力量打造微系统协同设计生态。

现阶段我国与国外射频微系统发展存在的差距主要有以下几点:

①射频微系统架构设计缺乏深入研究,各领域均缺乏统一的微系统体系评价标准。目前我国射频微系统成果往往以各个高校、研究所独立研发为主,缺乏统一组织、协同研究的成熟微系统设计架构与研发路线,对微系统产品许多方面的评价要求与方法尚无统一标准,容易出现研究功能重复、性能相近等问题;另外,对产品的检测和评价多方沟通流程复杂,且可能出现指标要求大大高于应用需求的指标浪费的情况。因此,有必要对射频微系统产品的架构设计进行深入研究,并规范射频微系统体系评价标准,建立规范化、通用化射频微系统技术平台。

②射频微系统核心元器件难以满足航天与武器型号任务以及民用领域应用,仍普遍存在核心芯片依赖进口的情况。在当前复杂的国际环境下,核心技术受制于人不仅会导致产品生产成本高,并且给武器的供货保障带来不稳定性;另一方面,可能存在的“芯片后门”也威胁着军品的安全性,使国防安全存在隐患。因此,迫切需要通过开展国内军用射频微系统设计研究,重点掌握相关集成技术,突破关键封装工艺瓶颈,打破芯片外部技术封锁,实现核心射频微系统器件的高可靠自主可控。

③射频微系统多物理场协同设计研究不足,技术攻关矛盾点较多。一方面,由于射频微系统通常尺寸较小、集成度高,因此往往功率密度较大、对散热性能要求较高;另一方面,不同的材料优势侧重点不同,往往很难平衡兼顾产品多种可靠性和电气性能,在技术上需要解决较多矛盾点。这就需要研究人员开展微纳尺度下的多物理场协同分析和设计,考虑多维度物理场下电磁场纠缠效应与趋肤效应、信号串扰、热–力–电耦合匹配等问题,提高产品整体性能。

6.2 我国射频微系统技术发展思考

结合国内射频微系统发展现状,对未来射频微系统技术发展思路提出了以下几点建议:

①对射频微系统进行系统需求与架构的深入论证,制定规范统一的射频微系统研发流程与评价标准,充分整合利用国内资源,形成以各大高校、工业部门研究机构以及军民企业为核心的射频微系统协同研发队伍,建立微系统异构集成支撑平台,发展协同创新、合力突破的微系统设计生态。

②优先发展国家最迫切需求的并能较快取得阶段性成果的射频微系统相关技术;重点攻坚突破射频微系统设计与多物理场协同仿真、三维异质异构集成、热管理与高可靠设计、微系统测试验证技术等射频微系统关键技术;鼓励支持推进射频微系统重要基础研究和核心技术自主创新。

③关注射频微系统方向核心人才培养,不断为射频微系统研发队伍注入高素质的新鲜血液,确保微系统持续有力地蓬勃发展。

7 结束语

射频微系统技术符合电子信息装备微型化、智能化、轻质化、多功能化、高性能化的永恒追求和发展趋势。从技术突破到产业发展,射频微系统技术已成为全球最具关注度、影响力和市场潜力的先进技术之一,未来必将推动军事与民用工业的颠覆性进步。为满足我国航天发射系列任务与新一代武器装备需要,应结合射频微系统发展趋势与系统需求,充分探索和利用微系统现有技术条件,在国家相关政策的大力支持下,通过对射频微系统技术总体布局、规范标准、协同设计、重点突破,在保障我国射频微 系统技术快速稳健发展的同时实现技术创新。

原文信息与来源:《射频微系统技术发展策略研究》 刘德喜,张晓庆,史磊,刘亚威,游月娟

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)