TMS320F206与CPU卡通信协议的优化

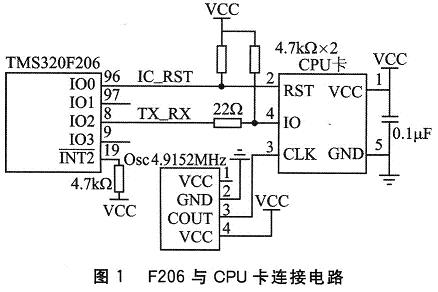

1 硬件电路

TMS320F206(简称F206)有1个通用输入引脚BIOS和1个通用输出引脚XF,此外还有IO0、IO1、IO2和IO3引脚,分别对应I/O状态寄存器的IO0~IO3。这4个引脚通过异步串行口寄存器(ASPCR)和I/O状态寄存器(IOSR)实现软件可控,可被单独配置成输入或输出。本文中使用IO0作为CPU卡(江苏意源公司iCos/Mil v1.0)的复位引脚,IO2作为CPU卡的I/O(输入/输出)引脚,电路图如图1所示。

2 软件实现

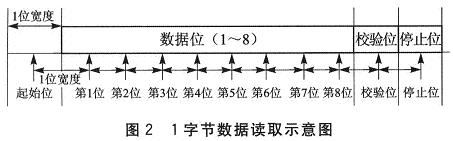

异步串行通信,传输协议bit流为:1位宽的低电平为起始位,8位宽的数据位,1位校验位,以及1位高电平的停止位。软件实现时,通过配置异步串行口寄存器(AS-PCR)和I/O状态寄存器(IOSR),并使用定时器功能,完成F206与CPU卡之间数据的发送与接收。

2.1 数据发送

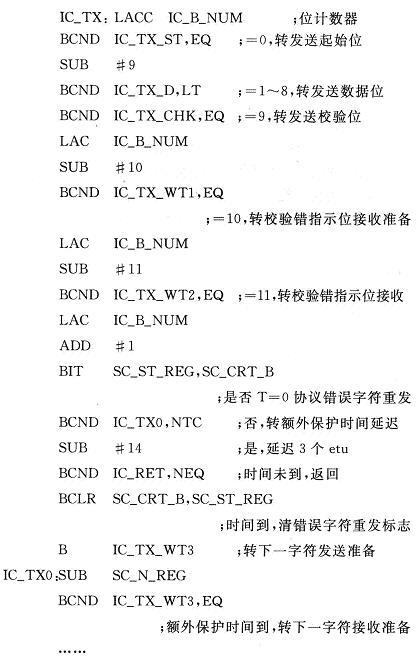

F206发送数据时,将IO2配置成输出状态,然后启动定时器,按照设置的波特率,分别将发送的数据按字节(8位)加上起始位、校验位和停止位发送给CPU卡的IO2口。

数据发送子程序为:

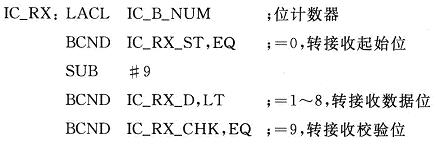

2.2 数据接收

接收数据一般采用软件轮询的方式实现。数据接收子程序为:

2.3 定时器设置

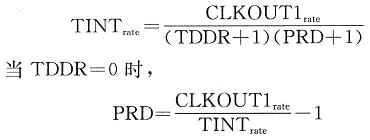

定时器中断频率由TDDR(定时器divide-down寄存器,定时计数寄存器TIM的低4位)和定时周期寄存器PRD共同确定。当两者都为0时,定时器中断频率为(CLKOUT1rate)/2;两者不全为0时,由如下公式确定:

举例:为了实现9 600 bps的有效传输速率,实际传输速率(额外增加1位起始位、1位校验位、1位停止位)应该为:

9 600 bps÷8×(8+1+1+1)=13 200 bps

故在晶振频率为20 MHz的条件下,PRD=20×106/13200-1=1514。

此时,将PRD设置为1514,每两次定时器中断的时间间隔即为1位数据的保持时问。一般来说,读取的时机靠近位宽的中间位置,读取的数据比较可靠和稳定,如图2所示。

3 软件改进

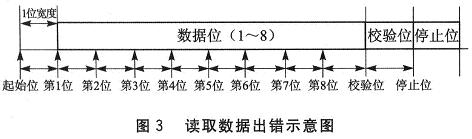

图2中,如果读取的起始位的位置正好处在起始位的开始,此时就会出现将起始位的末尾误判为第1位;或者读取的起始位的位置处在起始位的末尾,将可能丢失数据的第1位,都会导致读取数据出错,如图3所示。

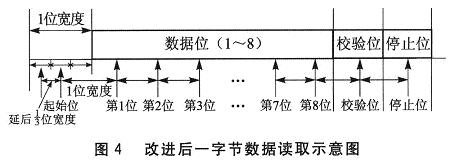

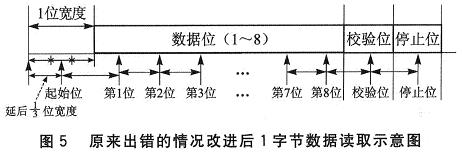

为了降低读取数据出错的概率,将起始位的判断周期定为位宽的1/3,并在检测到起始位后,继续等待1/3位宽(再等待一个定时中断),对起始位进行确认(读取的值为0)。此时才认定是一个正常的起始位,将定时周期修改为正常的位宽。此后每个定时器中断可以正确读取1位的数据,且保证了读取的时机处在1/3~2/3位宽的中间部分,如图4所示。

此时,图3中出错的问题也得到解决,如图5所示。

此外,还解决了毛刺引起的起始位误判的问题。因为一个毛刺的持续时间不会延续1/3位宽的时间,否则该应用将因稳定性太差而不能得到实用。

4 硬件改进

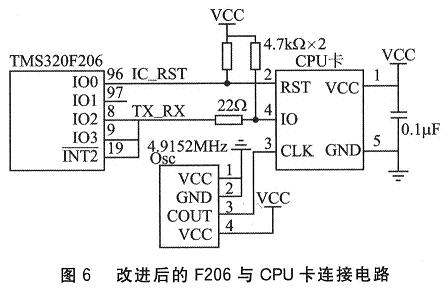

除了单纯使用定时器实现外,还可以结合INT2中断实现起始位的确认,电路如图6所示。

此时,建议延后1/3或者1/2个位宽时间,再读取起始位的状态。若还是为低电平,则作为一个有效的起始位,关闭INT2中断,然后按照一个完整位宽的时问启动定时器,每次读取1位,完成接收1字节后,关闭定时器,开启INT2中断,启动下一个字节的接收流程。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)