摘 要 :UART是广泛使用的串行数据通讯电路。本设计包含UART发送器、接收器和波特率发生器。设计应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

关键词 :FPGA/CPLD;UART;VHDL

UART(即Universal Asynchronous Receiver Transmitter 通用异步收发器)是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。

--- 串行外设用到RS232-C异步串行接口,一般采用专用的集成电路即UART实现。如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

一 UART简介

1 UART结构

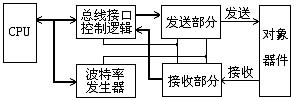

--- UART主要有由数据总线接口、控制逻辑、波特率发生器、发送部分和接收部分等组成。

--- 功能包括微处理器接口,发送缓冲器(tbr)、发送移位寄存器(tsr)、帧产生、奇偶校验、并转串、数据接收缓冲器(rbr)、接收移位寄存器(rsr)、帧产生、奇偶校验、串转并。

--- 图1是UART的典型应用。

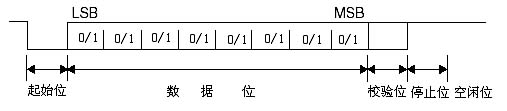

2 UART的帧格式

--- UART的帧格式如图2所示。

--- 包括线路空闲状态(idle,高电平)、起始位(start bit,低电平)、5~8位数据位(data bits)、校验位(parity bit,可选)和停止位(stop bit,位数可为1、1.5、2位)。

--- 这种格式是由起始位和停止位来实现字符的同步。

--- UART内部一般有配置寄存器,可以配置数据位数(5~8位)、是否有校验位和校验的类型、停止位的位数(1,1.5,2)等设置。

二 UART的设计与实现

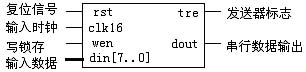

1 UART发送器

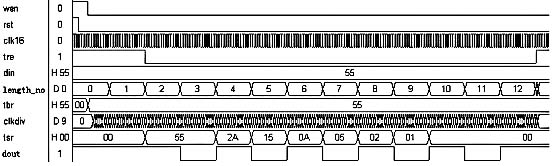

--- 发送器每隔16个CLK16时钟周期输出1位,次序遵循1位起始位、8位数据位(假定数据位为8位)、1位校验位(可选)、1位停止位。

--- CPU何时可以往发送缓冲器tbr写入数据,也就是说CPU要写数据到tbr时必须判断当前是否可写,如果不判这个条件,发送的数据会出错。

--- 数据的发送是由微处理器控制,微处理器给出wen信号,发送器根据此信号将并行数据din[7..0]锁存进发送缓冲器tbr[7..0],并通过发送移位寄存器tsr[7..0]发送串行数据至串行数据输出端dout。在数据发送过程中用输出信号tre作为标志信号,当一帧数据发送完毕时,tre信号为1,通知CPU在下个时钟装入新数据。

--- 发送器端口信号如图3所示。

--- 引入发送字符长度和发送次序计数器length_no,实现的部分VHDL程序如下。

--- if std_logic_vector(length_no) = “0001” then

--- tsr <= tbr ; --发送缓冲器tbr数据进入发送移位寄存器tsr

--- tre <= '0' ; --发送移位寄存器空标志置“0”

--- elsif std_logic_vector(length_no) = “0010” then

--- dout <= '0' ; --发送起始位信号“0”

--- elsif std_logic_vector(length_no) >= “0011” and std_logic_vector(length_no) <= “1010” then

--- tsr <= '0' & tsr(7 downto 1); --从低位到高位进行移位输出至串行输出端dout

--- dout <= tsr(0) ;

--- parity <= parity xor tsr(0) ; --奇偶校验

--- elsif std_logic_vector(length_no) = “1011” then

--- dout <= parity ; 校验位输出

--- elsif std_logic_vector(length_no) = “1100” then

--- dout <= '1' ; --停止位输出

--- tre <= '1' ; --发送完毕标志置“1”

--- end if ;

--- 发送器仿真波形如图4所示。

2 UART接收器

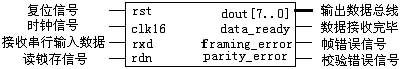

--- 串行数据帧和接收时钟是异步的,发送来的数据由逻辑1变为逻辑0可以视为一个数据帧的开始。接收器先要捕捉起始位,确定rxd输入由1到0,逻辑0要8个CLK16时钟周期,才是正常的起始位,然后在每隔16个CLK16时钟周期采样接收数据,移位输入接收移位寄存器rsr,最后输出数据dout。还要输出一个数据接收标志信号标志数据接收完。

--- 接收器的端口信号如图5所示。

--- 实现的部分VHDL程序如下。

--- elsif clk1x'event and clk1x = '1' then

--- if std_logic_vector(length_no) >= “0001” and std_logic_vector(length_no) <= “1001” then

--- --数据帧数据由接收串行数据端移位入接收移位寄存器

--- rsr(0) <= rxda ;

--- rsr(7 downto 1) <= rsr(6 downto 0) ;

--- parity <= parity xor rsr(7) ;

--- elsif std_logic_vector(length_no) = “1010” then

--- rbr <= rsr ; --接收移位寄存器数据进入接收缓冲器

--- ......

--- end if ;

--- 接收器仿真波形如图6所示。

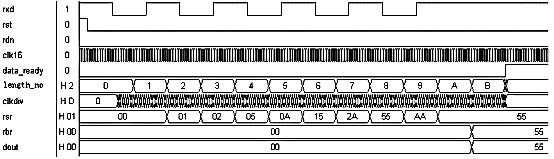

3 波特率发生器

--- UART的接收和发送是按照相同的波特率进行收发的。波特率发生器产生的时钟频率不是波特率时钟频率,而是波特率时钟频率的16倍,目的是为在接收时进行精确地采样,以提出异步的串行数据。

--- 根据给定的晶振时钟和要求的波特率算出波特率分频数。

--- 波特率发生器仿真波形如图7所示。

三 小结

--- 通过波特率发生器、发送器和接收器模块的设计与仿真,能较容易地实现通用异步收发器总模块,对于收发的数据帧和发生的波特率时钟频率能较灵活地改变,而且硬件实现不需要很多资源,尤其能较灵活地嵌入到FPGA/CPLD的开发中。在EDA技术平台上进行设计、仿真与实现具有较好的优越性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)