基于A/D转换器IC层叠并联实现通道倍扩展

1 引 言

A/D转换器是数据采集中常用的模/数转换器件,对于具有检测功能的智能仪表来说,设计者总希望在硬件电路板的最小面积内获得更多的检测通道。本文以MCS-51和ADC0804接口为例,在不增加A/D转换单元电路板面积的基础上通过三片ADC0804的IC(集成电路)层叠并联,使其模拟电压输入通道增加两倍,从而降低了硬件成本。

2 A/D转换器IC层叠并联的构思

ADC0804是常用的8位COMS逐次逼近寄存器、三态锁定输出、20脚双列直插、典型转换时间为100μs的A/D转换器。A/D转换器IC层叠并联是将三片同型号、同生产厂家、同批生产、测试完好的ADC0804芯片层叠并联,每片按引脚号一一对应焊接(模拟量输入VI+引脚和/CS引脚除外。字母左边的“/”表示低电平有效,下同)。实现IC层叠并联后, 模拟量输入通道由原来的单路扩展为三路,在不增加A/D转换单元电路板面积的同时,使A/D转换通道数量增加两倍。

3 A/D转换器IC层叠并联设计实例

3.1 硬件接口电路设计

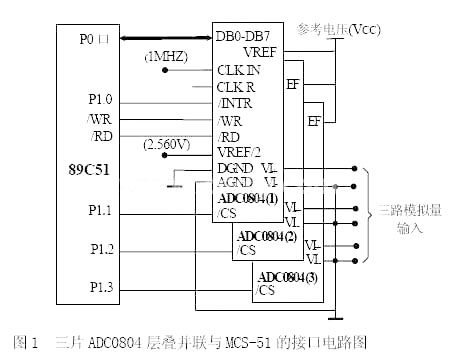

将三片ADC0804层叠并联,按照各引脚的逻辑要求施加电平并进行A/D转换,测试后可知,0804(1)、0804(2)、0804(3)具体哪一片能向单片机输出转换后的数字量数据,关键取决于该芯片的输出允许信号(/CS)端是否有效(低电平有效)。由此可见,只要对三片ADC0804的/CS端进行分时控制,即可分别实现各自的A/D转换功能。ADC0804带有锁存器,可直接与89C51芯片进行连接。三片ADC0804层叠并联与MCS-51的接口电路图,如图1所示。

3.2 三路模拟通道分时控制原理分析

MCS-51与ADC0804接口进行单通道转换时的过程是:当ADC0804的片选信号/CS有效时,施加一个启动信号/WR,转换器将自动进行转换。转换结束后,数据被锁存器锁存,同时发出/INTR信号。此后,又在/CS有效时施加一个/RD信号,即可把转换的结果从锁存器中读出。

图1中0804(1)、0804(2)、0804(3)三个芯片的引脚除每片的模拟量输入VI+和/CS引脚外,其余均按引脚号一一对应连接,具体选择哪个芯片输出允许,取决于该芯片是否能被选中(/CS是否有效)。在0804(1)被选中并完成A/D转换功能的过程中,只允许 0804(1)的/CS端为低电

平,使得0804(1)的/WR、/RD和/INTR端均能按时序控制正常工作, DB0-DB7的数字数据才有输出。此时0804(2)、0804(3)的/CS端必须为高电平,以保证这两个芯片的数据端DB0-DB7为高阻态,否则三个芯片的数据将相互扰乱。同理,当0804(2)被选中并完成A/D转换功能时,0804(2)的/CS端为低电平,此时0804(1)、0804(3)的/CS端必须为高电平,对于0804(3)亦然。

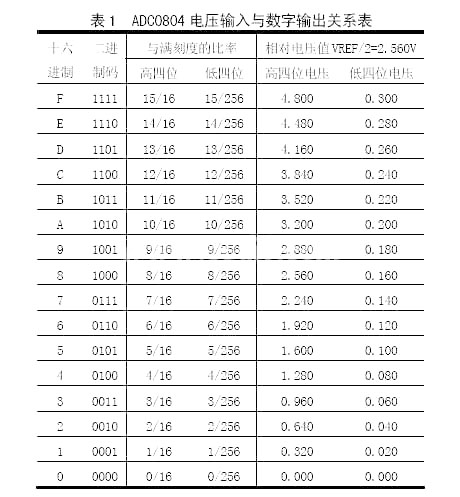

ADC0804的时钟频率约限制在100KHZ—1460KHZ。P1.1 、P1.2 、P1.3 分别作为0804(1)、0804(2)、0804(3)的片选分时控制信号;P1.0用作分时接收三个A/D芯片的中断请求输出/INTR信号。本例采用单极型连接方法,故三路模拟量输入的VI-端均接地。ADC0804电压输入与数字输出关系表,如表1所示。

3.3 软件应用设计

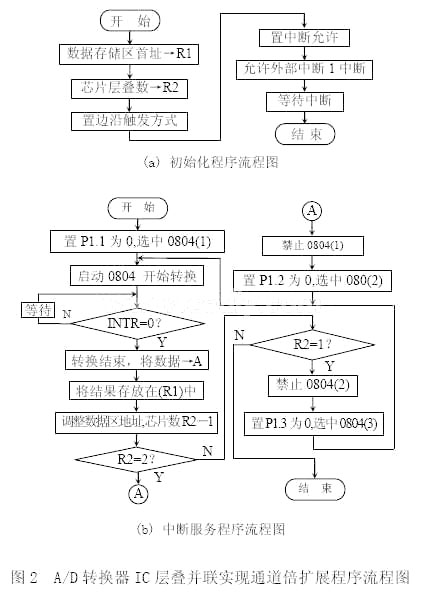

设有三路模拟量输入的检测系统,每路电压分别为1.000V、2.000V、3.000V,采样后的数字量数据依次存放到60H—62H的3个内存单元中。该程序以中断方式进行数据传送,P1.1 、P1.2 、P1.3 分别对0804(1)、0804(2)、0804(3)分时选通;P1.0分时接收三个A/D芯片的中断请求输出信号。/INTR信号把转换完成的状态作为单片机的中断请求信号。A/D转换器IC层叠并联实现通道倍扩展程序流程图,如图2所示。其中,图2(a)为初始化程序流程图,图2(b)为中断服务程序流程图。

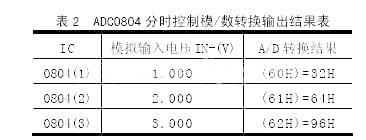

3.4 分时控制模/数转换输出结果分析

ADC0804分时控制模/数转换输出结果表,如表2所示。

程序执行后,60H单元的A/D转换结果为32H,对应的十六进制高半字节为3H,低半字节为2H,通过表1可查得分别对应的高半字节和低半字节电压为0.960+0.040=1.000V;61H单元的A/D转换结果为64H,对应的十六进制高半字节为6H,低半字节为4H,通过表1可查得分别对应的高半字节和低半字节电压为1.920+0.080=2.000V;62H单元的A/D转换结果为96H,对应的十六进制高半字节为9H,低半字节为6H,通过表1可查得分别对应的高半字节和低半字节电压为2.880+0.120=3.000V。

结论:以上三个单元的A/D转换数字量结果均分别与相对应的模拟输入电压相吻合,此结果表明ADC0804A/D转换器IC层叠并联实现通道倍扩展的设计方案是成功的。

4 结束语

此文相关技术已获中国国家专利,其创新点:采用A/D转换器IC层叠并联,在不增加A/D转换单元电路板面积的同时,使A/D转换通道的数量增加两倍,降低了硬件成本。

该项技术还可进一步推广到三片以上ADC0804 A/D转换器或其它特性IC芯片的层叠并联中去。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)