关键词:增强型并行端口(EPP),移位寄存器输出,CPLD,Verilog HDL

1 引 言

由于ISA总线插槽在台式机中逐渐减少,甚至消失,微机控制系统中越来越多地利用并行口进行数据传送。增强型并行端口EPP(Enhanced ParallelPort)不但与传统的标准并行端口(SPP)兼容,而且传送速率可以达到500k~2Mbyte/s(相当于ISA总线的传送速率),特别是EPP提供了硬件握手信号,为软硬件设计提供了方便。因此,工业控制中基于EPP的应用日益广泛。

一些诸如热印头,LED显示驱动器等点阵控制器件,由于控制点数多,一般使用移位寄存器接收数据。若采用并行I/O口产生移位寄存器输出数据和同步脉冲,通常需要多个I/O读写周期。这里介绍一种利用EPP并行端口扩展移位寄存器输出接口的方案,可在一个I/O读写周期完成一个字节的输出,达到高速传送的效果。

2 EPP协议简介

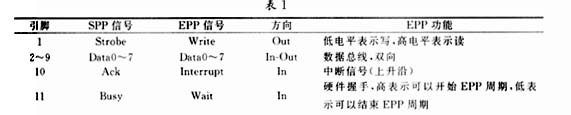

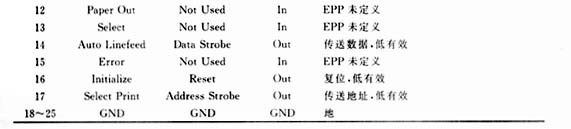

EPP协议是IEEE1284中规定的一种双向传送并行接口,它保持了与标准并行口(SPP)的兼容性。表1是SPP和EPP的引脚定义及其功能。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)