目前业界对于DDR模块(一驱多)的端接电阻的摆放位置,就好像差分线对内要做等长,高速信号不能走直角,25G信号不能有很长的过孔stub一样,是一种SI常识性的范畴了。所以如果你遇到了一个DDR模块的端接电阻摆放错位置时,你觉得会怎么样?

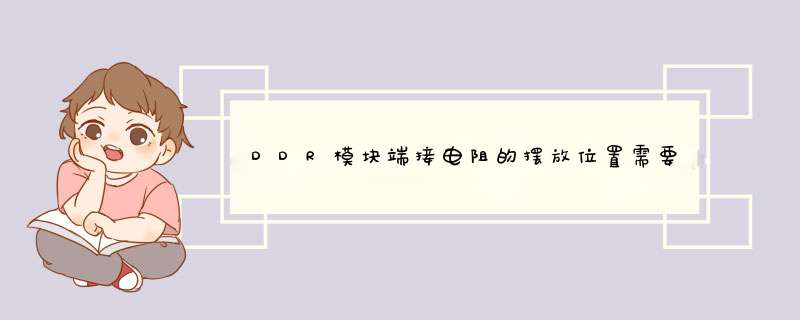

前面说的关于一驱多的DDR模块端接电阻的摆放位置是一个SI的常识,我们都会把它摆放在最后一个颗粒处,就像下图这样。

DDR端接电阻放在末端,大家会说,这种错误应该没人会犯了吧?很不巧,我们高速先生见过很多很多的案例,刚好有一个案例是连这种规则都违反的,而且还不是在设计阶段,是已经生产出来的板子……

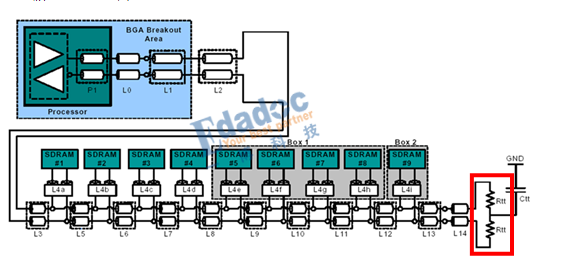

这是一个1拖4的DDR3模块,客户的目标是跑到800M,结果发现只能跑到400M,高速先生也本以为会是一个很难定位问题和优化的设计,结果把客户的板子一拿过来看,结果竟是犯了这样的错误。把端接电阻都放在了第一个颗粒的位置,如下图的时钟信号的拓扑,红色框框是端接电阻。

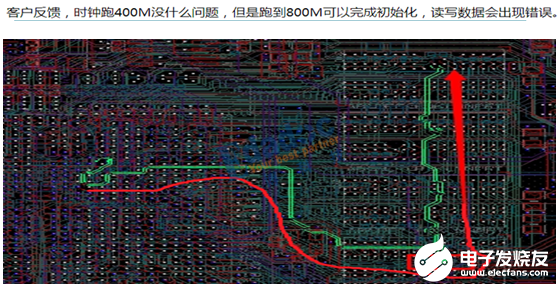

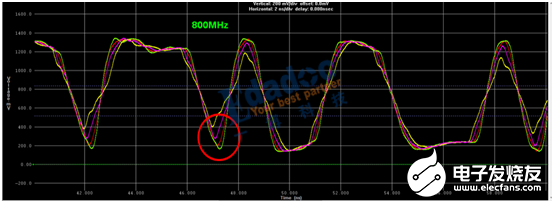

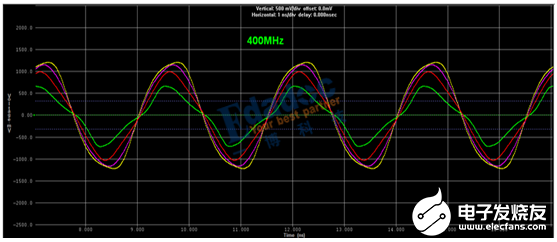

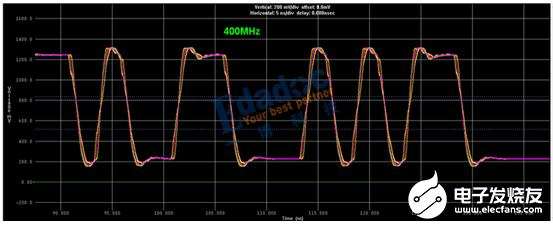

我们第一步要做的是从仿真上去验证测试结果,我们分别对800M的时钟和地址信号做下仿真,结果的确很符合测试的情况。

时钟信号在颗粒2是完全fail的,而地址信号也是裕量非常的小。另外客户说能跑400M,我们也仿真看看400M的情况。

恩,400M的话从仿真来看,无论是时钟信号还是地址信号都有一些裕量,测试能OK也是有可能的。

这个板子的问题和解决方法是都非常清晰的,在我司重新进行改板设计后,把端接电阻放回到它应该在的位置上,测试800M就没有任何问题了。这个案例是“血”的教训告诉我们,有的规则是不能随便更改的,尤其是已经得到业界公认的规则,不然设计加工出来等待你们的就只有fail了。本期的文章就这么简单,希望能对大家有一定的启发。

编辑:hfy

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)