基于DSP和FPGA的通用图像处理平台设计

摘要:设计一种基于DSP和FPGA架构的通用图像处理平台,运用FPGA实现微处理器接口设计,并对图像数据进行简

单预处理,利用DSP进行复杂图像处理算法和逻辑控制,实现图像数据的高速传输与实时处理。系统可应用于贴片机芯

片检测中,并进行性能评估实验。实验表明该系统满足实时性和功耗的设计需求,易于维护和升级,具备较强的通用性。

关键词:数字信号处理器;现场可编程门阵列;数字图像处理:DSP/BIOS

1 引言

随着数字化技术不断发展和完善,数字图像处理技术已广泛应用于工业、军事、生物医疗、电信等领域。实际应用中能够运行复杂灵活的图像处理算法和大数据量的数据传输处理能力成为图像处理平台稳定运行的前提,而系统实时性、体积、功耗等因素也至关重要。传统数字图像处理平台大多采用通用PC机、高速图像采集卡和基于VC++的软件平台来实现,但很难满足当前对系统体积、功耗和实时性要求。因此这里提出的基于DSP和FPGA的通用图像处理平台,充分发挥FPGA灵活性强和DSP运算速度快、寻址方式灵活的优点,更好地提高图像处理系统的集成度,降低系统功耗,并满足实时性要求。

2 高速图像处理平台的工作原理

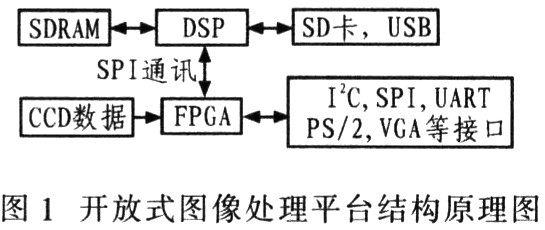

为实现高速图像的实时处理,该系统采用DSP和FPGA线性流水线阵列结构,将FPGA可在通用接口设计和简单信号处理等方面的优点与DSP的快速数字信号处理能力相结合,充分发挥这两者的优点。该系统主要由DSP和FPGA的子系统构成,为保证大量图像数据流快速稳定通讯,DSP与FPGA间通过外扩的SDRAM实现大容量数据交换。DSP子系统则实现较为复杂的图像处理算法,并提供图像存储功能。而FPGA子系统完成CCD传感器图像数据的预处理以及微控制器通用接口功能。

系统结构原理图如图1所示。CCD传感器输入的图像数据经FPGA预处理后,将数据传送至DSP,DSP对输入数据进行实时图像处理,并将处理后的图像通过EMIF接口发送并保存至外扩SDRAM。同样,FPGA也能够读取外扩SDRAM的图像数据,通过VGA接口实时显示。对于少量数据流,如系统参数或图像数据传输的起止信息等,则通过SPI接口实现。DSP子系统内部扩展有SD卡接口和USB主机接口,主要用于图像数据的存储和传输等。FPGA子系统外扩的主要接口包括:I2C、SPI、UART、PS/2和VGA等接口,用于系统升级和调试,提高系统通用性。

3 系统硬件结构设计

系统硬件设计采用模块化设计思想,将整个系统分为DSP子系统和FPGA子系统。这两者间的数据交换通过双端口RAM方式实现。

3.1 器件选型

该系统设计选用TI公司的TMS320VC5509A型DSP。该款DSP功耗低,片上资源丰富,主频最高可达200 MHz,片上带有128 K×16 bit RAM和32 K×16 bit ROM,内置6个DMA通道,1个I2C接口,3个McBSP接口,1个RTC模块,其外部存储器接口(EMIF)能与SDRAM无缝连接,同时还带有USB接口。FPAG选用ALTERA的Cyclone-II系列处理器,具有强大的逻辑处理能力,从而实现微处理器通用接口设计和简单信息预处理功能。

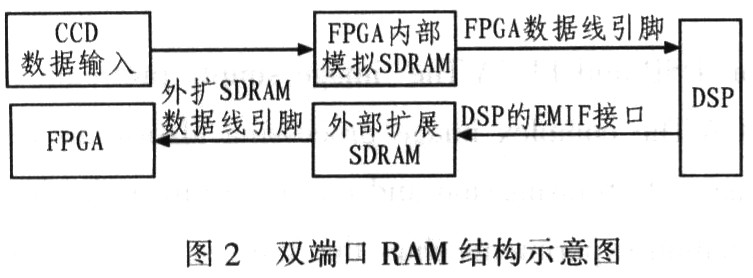

3.2 DSP与FPGA的接口设计

为保证系统实时性,DSP与FPGA之间的接口需实现大数据流通讯流畅的功能。将FPGA内部结果缓冲器模拟为SDRAM接口,一端输入CCD图像信号,一端输出图像数据并连接至DSP数据线。DSP的EMIF接口外接一片4 M×16 bit的SDRAM MT48LC4M16A2-75,通过将处理后的图像数据回传至外扩SDRAM,由FPGA实时读取并通过VGA接口显示,从而实现DSP与FPGA之间数据通讯功能。这两者之间配置的双端口RAM连接如图2所示。

3.3 DSP子系统

DSP子系统主要包括电源管理单元、EMIF接口、SD卡接口、USB接口、JTAG调试接口和引导装载(Bootload)电路等。电源管理单元主要为系统提供稳定电源;EMIF接口主要用于外部扩展存储器;SD卡接口用于掉电后图像数据的存储;USB接口用于外接其他外设;JTAG接口用于电路调试等。

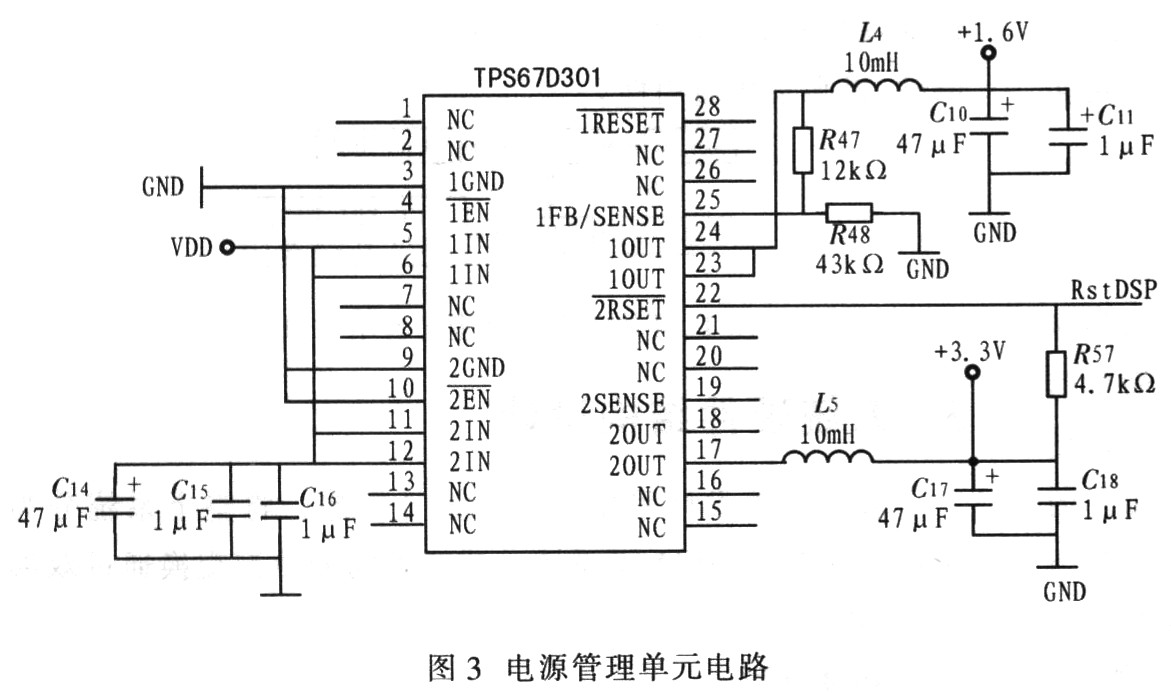

3.3.1 电源管理单元

DSP子系统供电可分为1.6 V和3.3 V两种,DSP内核需1.6 V供电,外设及I/O端口采用3.3 V供电,并需保证内核先于I/O上电,I/O先于内核掉电。该系统采用电源器件TPS767D301配置不同电压值。该器件包括两路电压输出,每路最大输出电流可达1 A.输出电压稳定。图3为电源管理单元电路。

3.3.2 外部存储器接口

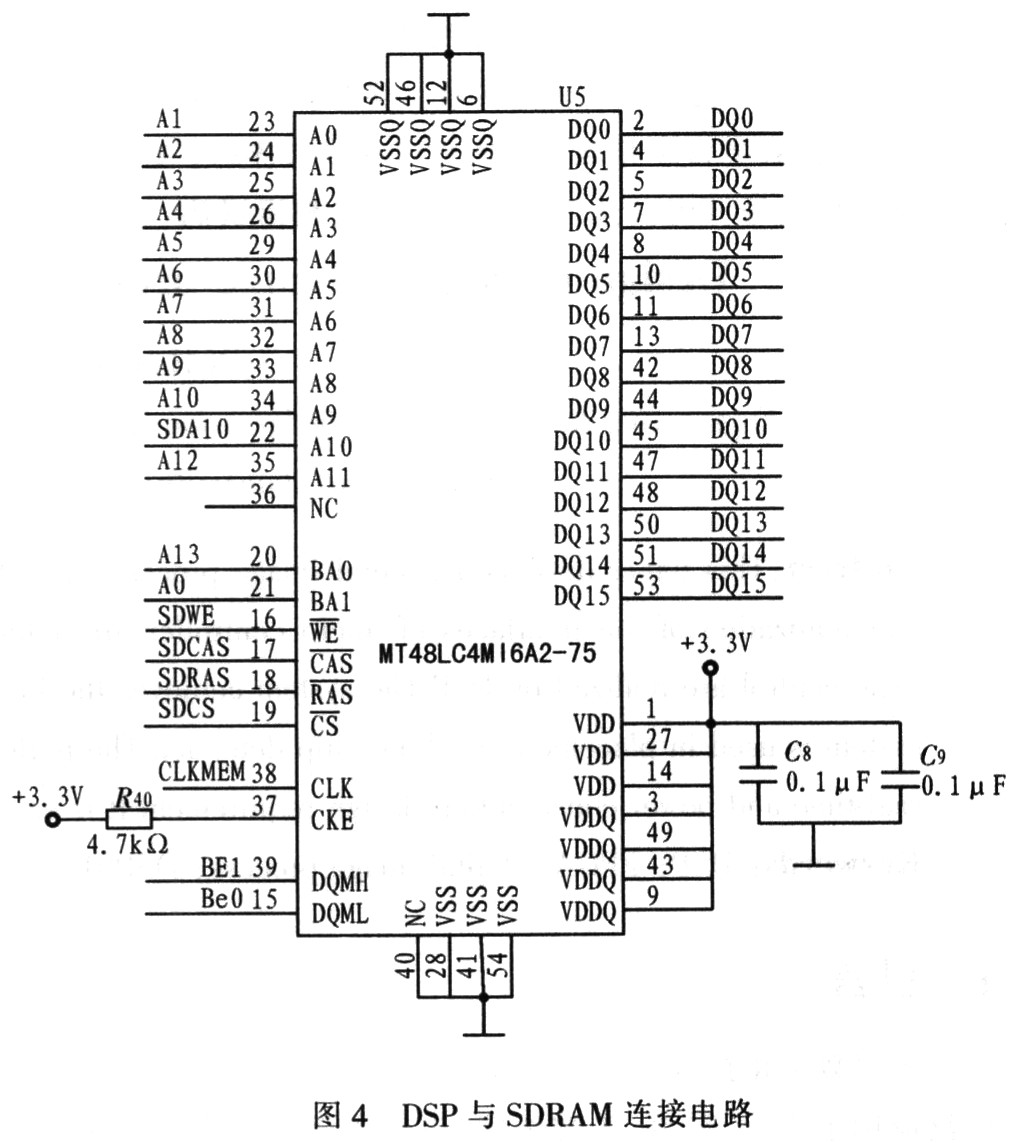

TMS320VC5509A内部集成的EMIF接口除了支持异步存储器,还支持同步突发静态存储器(SBSRAM)和同步动态存储器(SDRAM)。在此通过编程寄存器配置EMIF和SDRAM的连接。设置CE空间控制寄存器1的MTYPE=011b表明连接存储器是SDRAM。图4为配置的4 M×16 bit的SDRAM MT48LC4M16A2-75的连接电路。由于单个CE空间的限制是4 MB,故使用2个CE空间,并将CEO引脚作为片选,CE1引脚悬空。外扩的SDRAM主要用于存储处理后的图像数据。

3.3.3 SD卡接口

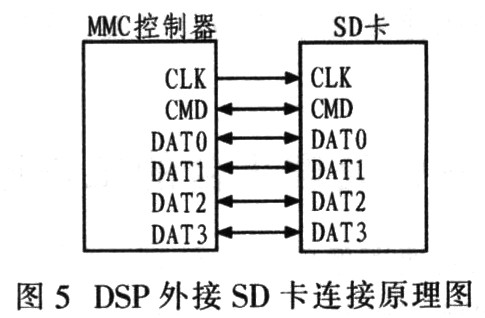

TMS320VC5509A内置MMC控制器支持对MMC卡和SD卡的读写,支持MMC/SD协议和SPI协议,MMC控制器的运行频率可通过程序设置,并与McBSP接口引脚复用,使用时需设置外部总线选择寄存器(EBSR)。图5所示为MMC控制器与SD卡信号连接图,连接信号有:时钟信号(CLK)、控制信号(CMD)和数据信号(DAT0~DAT3)。

3.3.4 Bootload电路

Bootload的功能是在系统上电后,将用户程序从片外的慢速存储器加载至片内RAM中,并使其高速运行。这里选用EEPROM作为外部非易失性程序存储器。TMS320VC5509A的Bootload方式支持EMIF模式,SPI模式和McBSP模式等。其中SPI模式的EEPROM自举有两种,一种是基于16位字节地址,最大可达64 K寻址空间;另一种是基于24位字节地址,最大可达16 M寻址空间。在此选用第一种方式,并引出Bootload模式选择引脚BOOTM[3:0],便于系统升级。

3.4 FPGA子系统组成及功能

为实现该图像处理平台通用性和实时性,FPGA子系统需实现的功能包括:开放式的图像数据采集总线,DSP图像处理实时数据总线,100 MB以太网接口,UART接口,VGA实时显示模块,I2C存储器接口和PS/2接口等。其中UART接口方便系统软件开发及调试,VGA接口用于图像数据实时显示,I2C接口外接EEPROM用于系统参数的掉电存储。为实现多个系统的网络化,FPGA子系统还设有以太网接口,用于多个系统将处理结果回传至PC端口。PS/2接口为预留端口,后期根据需要增加键盘等输入设备。

4 系统软件设计

4.1 软件开发开具

该系统软件设计采用TI公司CCS3.1(Code ComposerStudio)作为开发环境,并利用CCS自带的DSP/BIOS实时 *** 作系统进行设计。在CCS中完成软件的编辑、编译、调试、代码性能测试和项目管理等工作。通过使用DSP/BIOS提供的一系列丰富的内核服务,快速创建满足实时性能要求的精细复杂的多任务应用程序。DSP/BIOS内核具有跨平台的标准API接口,能被用户程序调用,易于移植。此外,这些服务除支持多线程调度管理外,还支持系统实时分析以及资料管理。DSP/BIOS内核具有很大的尺寸伸缩性,多线程配置下的内核镜像的代码量最小仅有1 K字,占用DSP资源非常少。

4.2 软件系统总体设计

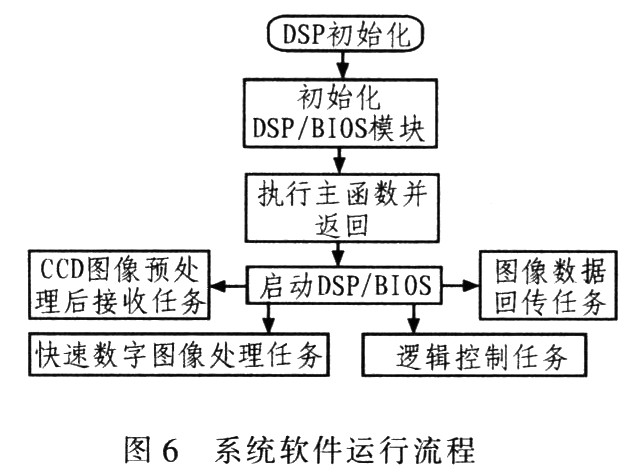

在硬件平台基础上,利用CCS集成开发环境中的DSP/BIOS实时 *** 作系统内核,开发具有可扩展性的软件系统。系统软件部分采用模块化和层次化设计思想。软件结构主要包括:设备驱动层、 *** 作系统层、应用程序接口(API)层和应用层。设备驱动层负责与硬件有关的各个模块或外设的驱动程序设计; *** 作系统层负责嵌人式实时 *** 作系统移植;应用程序接口层完成系统控制功能、数据读写等,并实现硬件无关性;应用层则设计与系统应用背景有关的控制程序。图6为系统软件运行流程。软件设计主要分为CCD图像预处理后的接收任务、快速数字图像处理任务、逻辑控制任务和图像数据回传任务。系统上电后,程序首先执行DSP的初始化和DSP/BIOS初始化,接着执行函数主体并启动DSP/BIOS *** 作系统,以后的任务均由 *** 作系统进行调度。采用嵌入式实时 *** 作系统DSP/BIOS构建的图像处理软件平台能较好满足任务对实时性的要求,且结构稳定紧凑,可移植性高。

5 实验结果

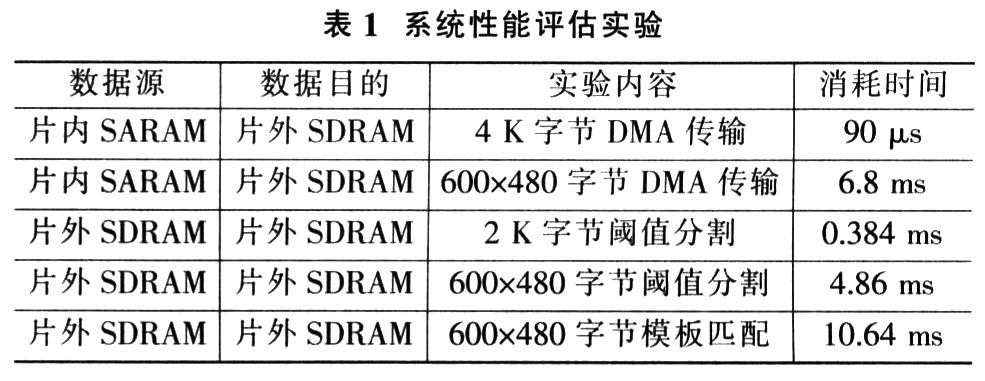

为验证该系统的通用性与实时性,将其应用于某型号贴片机的器件检测中,并进行以下3个实验:DMA方式下大容量数据传输实验,阈值分割测试实验和模板匹配测试实验。其中DMA方式下大容量数据传输实验,通过DMA方式将片内数据传输至片外SDRAM内部,图像大小为600×480字节。阈值分割和模板匹配实验则直接读取片外SDRAM中的图像数据,并对图像分别进行阈值分割和8×8模板匹配实验,图像处理算法采用TI公司图像处理库甬数。IMG threshold()和IMG_mad_8×8()。设置DSP运行时钟为208 MHz,采用定时器0计时,DMA通道选用通道0,图像数据大小为600×480字节。实验结果如表1所示。

以上实验数据表明,当采用600×480面阵CCD数据采集,并要求每帧图像处理时间限定在30 ms以内时,该系统能很好满足当前系统需要。

6 结论

系统能够满足600×480面阵CCD和普通线阵CCD传感器对系统处理能力的需要,具有较强的通过性和实时性。其设计创新之处在于,充分运用DSP的强大运算能力和灵活的寻址方式,结合FPGA在通用接口设计和简单信号处理速度方面的优点,采用基于DSP/BIOS的软件架构,使得系统集成度高,功耗低,具备更高的实时性和可移植性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)