随着消费者要求新产品定期增加功能或提高应用灵活性,开发人员对修改系统应用功能的快捷性和简便性要求越来越高。从存储器角度看,这预示着可能需要用性能更高、合格检测更快的先进产品更换现有产品。新一代非易失性存储器应具备各种参数微调功能,能够缩减应用电路板的工程周期。

1.应用灵活性

不同应用在不同的容性负载下需要不同的工作频率,这项要求与芯片组的性能以及电路板布局和复杂性紧密相关。例如,高频工作环境通常对电性能的优化要求严格,设计工程师需要考虑整个电路板上的电噪声,以降低线路的寄生电容。在这种情况下,降低存储器输出驱动器的强度更加受欢迎。此外,还必须根据工作频率优化指令执行速度。有时候,要想在发送命令后取得适合的高效的吞吐量,就必须减少空时钟周期次数。

2.测试/最终使用

设计人员应该优化存储器,以缩减系统上电期间的代码读取和下载时间。在新的先进的平台上,如车用电子、计算机光驱或蓝牙模块,SPI闪存可能用于直接从非易失性存储器读取部分系统固件,以缩短系统固件下载到高速易失性存储器的过程。当然,目前出现的最新应用对存储器的灵活性要求更加严格,本文稍后再做详解。

3.XiP自适应模式

SPI闪存的的优点是引脚数量少而且固定不变(8个或16个)。串口闪存的这个特性可简化电路板布局,无需更改硬件即可升级固件,从而可以降低系统开发的总体成本。

由于在简易性和成本方面的强大优势,PC机和消费电子市场出现了并口闪存改用SPI闪存的发展趋势。只要达到性能要求时,设备厂商就会优先选用串口闪存。计算机光驱、汽车电子、蓝牙模块、机顶盒和调制解调器市场正在引入这种能够把代码直接读到非易失性存储器内的SPI闪存。

XiP(片内执行)应用要求串口存储器提供一种“随机访存”仿真功能,即无需发送指令即可访问存储器内容,并准许以最大的吞吐量访问存储器。因为传统用途是存储和下载代码,所以SPI存储器是同步器件,XIP功能迫使设计人员研发灵活的存储器,能够根据芯片组特性灵活地配置串行闪存。例如,在系统上电后,具有XIP功能的器件需要基于命令、地址和数据的JEDEC协议,所以有些逻辑器件不准像管理XIP器件一样管理串口闪存。

此外,有些逻辑器件只在一条线上或者最多在两条线上支持XIP模式,因为固有的硬件限制,不可能开启4位I/O输入输出模式。

最后,因为实现一个混合协议、接受命令的传统存储器和不接受命令的非传统存储器的设计困难,芯片组厂商更愿意保留原有的SPI指令结构,即命令、地址和数据。在这些情况下,高速协议结合并行化命令、地址和数据的方案更受市场欢迎。

选择正确的存储器架构

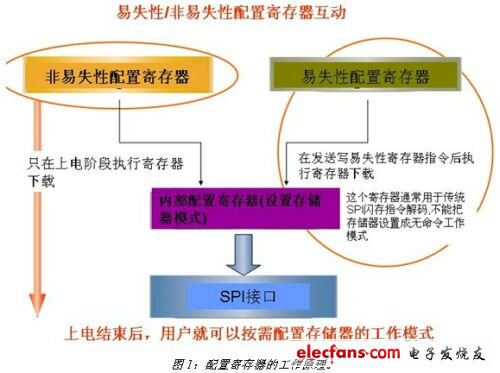

通过在新一代SPI闪存架构内引入易失性和非易失性配置寄存器,可完全满足设计人员对串行闪存的灵活性要求,使闪存适合嵌入式市场最新平台的应用环境。通过引入这两种寄存器,最终用户能够根据平台的需求配置存储器。图1简要介绍了配置寄存器的工作原理。

在标准SPI存储器内,命令被直接送到一个具有指令解码功能的内部寄存器内,该寄存器与状态寄存器和内部状态机互动。每次上电后,标准SPI存储器将只接受命令,以便正确地执行读写擦除 *** 作。相反,在采用配置寄存器的SPI存储器架构中,所有 *** 作都可以通过这些工具过滤。

在默认模式下,存储器将是一个传统存储器。但是,你可以根据应用需求任意配置存储器。例如,你可以设置寄存器的右边部分,强制内部寄存器无命令工作且只接受地址。可以通过非易失性寄存器或易失性寄存器选择这种 *** 作模式。如果使用非易失性寄存器选择 *** 作模式,必须在一次掉电/上电周期后,存储器才能进入所需的工作模式。表1是配置寄存器内容的示例。

使用适合的命令读写配置寄存器。在上电后,存储器的内部状态机将检查非易失性配置寄存器的内容,并根据写入该寄存器的信息执行下一项 *** 作。

1.高速 XiP示例

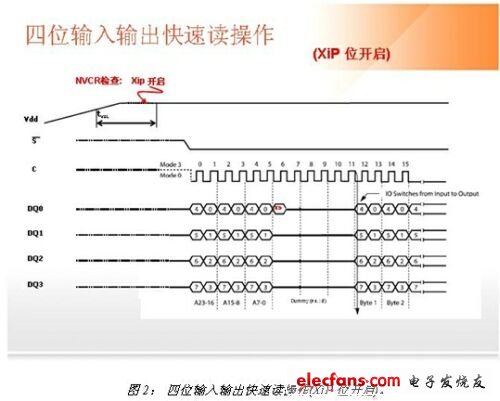

如果“XiP enabled at power on”(上电开启XIP模式)位被置入正确数值,存储器将只接受地址,无需对指令进行解码。因此,在上电结束后,存储器将立即变成一个随机访问存储器,并支持芯片组设计的最高总线速度。存储器可以支持四位I/O和两位I/O输入输出模式,可以在接收数据前设置适合的空时钟周期数(图2)。

2.测试阶段配置灵活性的优点

因为配置寄存器的灵活性,用户还可以选择另一个功能。存储器可以分成两个主要设置。第一个设置主要用于应用测试阶段。在这个阶段,所有的指令都必须可用,以全面检测电路板以及存储器的功能。此外,可以临时让存储器工作环境受应力作用,例如,减少时钟周期次数且/或提高输出缓冲的强度,以改进线路负载情况的匹配性。

可以通过易失性配置寄存器查找最佳的存储器设置。当发现最佳的条件时,设置信息可能会保存到非易失性配置寄存器内。在下一次系统上电后,创新的SPI存储器将进入所需的工作模式,这实际上就第二个(最终)设置,在此模式下,存储器的工作方式完全不同于测试阶段。

如前文所述,在最终应用中,存储器不再是一个传统的SPI存储器。如果微控制器将闪存指定为仅高吞吐量的读取数据,则可以有效地去除标准SPI存储器的指令解码阶段。此外,在非易失性配置寄存器内写入一个适合的位,还可以缩短上电时间。

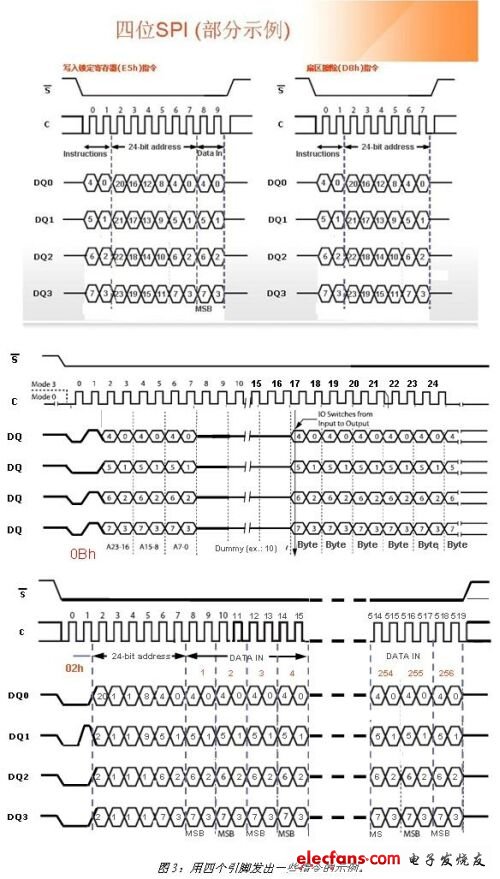

3.单线、双线或四线指令协议

配置寄存器的最大亮点是,除工业标准的单线命令协议外,还可以通过两个或四个引脚发送8位指令代码来控制SPI闪存。在SPI闪存的全程工作阶段(命令、地址和数据),微控制器能够与位信息交换并行化的存储器互动,这个时候,微控制器就需要这个双线或四线命令传送功能。图3给出了用四个引脚发出一些指令的示例。

表2列出了当芯片组不需要发送指令代码时每个协议缩短的随机访问时间。

配置寄存器的灵活性

由于内置配置寄存器,存储器可以设置成5个不同的XIP模式,能够适合特定的应用需求和性能,通过节省指令时钟周期开销来缩短存储器随机访问时间。这个改进的性能可用于XIP应用,直接在SPI闪存内执行代码,无需把代码下载到RAM存储器。

为提供最佳的应用灵活性,N25Q闪存可通过两种方法进入XIP模式。第一种是非易失性配置方法,我们推荐在直接启动系统进入所需的XIP模式的最终应用中使用这种方法;第二种是易失性配置方法,我们建议在启动系统进入存储器标准模式的应用中使用这种方法。

由于配置寄存器提供的可选配置功能,这款产品是市场上首个提供这两种配置方法的四位I/O解决方案。除嵌入式系统的传统的3V Vcc 电压范围外,很多供应商开始提供无线应用需要的1.8V SPI闪存(还需要特别关注能效)。

为什么SPI闪存内置配置寄存器?

SPI闪存解决方案的主要优点是引脚数量少,可以简化电路板布局,降低系统总体成本,实现非常空间紧凑的解决方案。此外,不同的存储容量共用同一协议和引脚配置,使存储器容量可以自由扩减,并支持在一条总线上连接不同的器件。

与并行闪存相比,传统的SPI闪存解决方案的典型缺点是随机访问时间过长,因为SPI是一个固定、缓慢的同步协议,所以应用灵活性不高。配置寄存器架构的目的是克服传统SPI闪存的两大缺陷,同时保留原有优点。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)