电路功能与优势

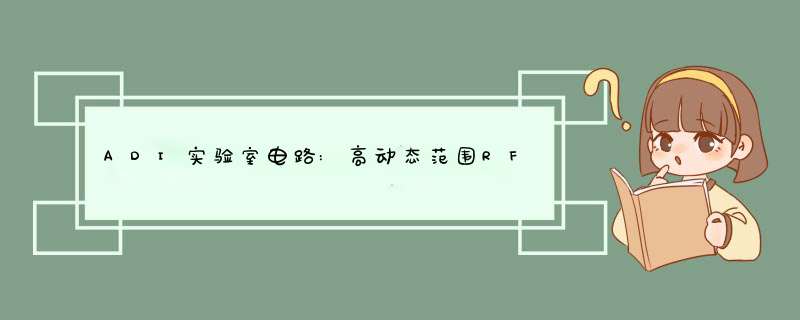

将 ADRF6702 IQ调制器和 AD9122 16位双通道1.2 GSPS TxDAC结合使用可满足现代高水平QAM或OFDM无线发射器(如图1所示)的动态范围要求。该电路的动态范围出色,足以同时支持ZIF(零中频/基带)和CIF(最高200 MHz至300MHz的复合中频)。AD9122可选最高8×插值和一个32位NCO,以获得超精细中频灵敏度。

发射器的整体性能和直接组成信号链的组件动态范围息息相关。在使用DAC和IQ调制器的混合信号发射器中,这类组件的本底噪声和失真特性决定了信号链的整体动态范围。但是,DAC的本底噪声也可能由于采样时钟抖动而变得更严重,而且IQ调制器性能取决于其本地振荡器(LO)的噪声和杂散特性。因此采样时钟和LO发生采用高性能组件是高性能发射器的关键所在。

此外,在PCB板上尽量靠近DAC和调制器的位置产生这些信号并使用一个外部参考源也可大大简化设计。单独产生采用时钟和LO(LO绝大多数为数GHz信号)并且与DAC和IQ调制器保持一定距离,要求十分谨慎地处理PCB布局。哪怕最细微的布局错误都可能会引起这些关键信号发生耦合,并降低整体信号链性能。

信号链性能也很大程度上取决于DAC/ IQ调制器接口滤波器。为优化性能,建议在仔细分析所需系统规格后再设计这款无源滤波器。

ADRF6702包括一个板载分数PLL用于LO生成,这样只需一个低频参考(一般低于100 MHz)即可合成IQ调制器LO。在AD9516 时钟发生器内使用PLL允许一个参考同时为ADRF6702产生DAC采样时钟和PLL参考。

图1中的电路使用AD9516-0构建而成,也可选用AD9516系列的其他产品,具体取决于所需的内部VCO频率。

图1. AD9122、ADRF6702和AD9516用于高动态范围发射器

电路描述

配有内部LO合成器、合成器IQ调制器接口的ADRF6702 IQ调制器

ADRF6702 IQ调制器是一种具有多种特性的独特器件。除出色的动态范围外,它还包括一个分数-N PLL,允许编程设置低于25 kHz的离散LO频率步进,同时仍保持足够小的整体频率倍增以避免从参考到合成器输出的相位噪声激增。

ADRF6702的另一特点是IQ调制器的2分频架构。传统IQ调制器接受1倍所需LO的LO输入频率。在内部,分布式RC网络从单LO频率输入产生所需的同相和正交LO信号。因为这属于无源RC网络,所以实现正交调制精度的带宽有限。而且,为获得出色的正交精度,外部LQ应保持频谱纯净。这种传统LO调制器架构在LO上所产生的谐波可能会降低整体调制精度。为此,当使用PLL合成器来产生IQ调制器所需的LO信号时,往往需要在IQ调制器LO输入端配置一个窄过渡带的带通或低通滤波器。

在ADRF6702的2分频LO架构中,内部使用一个简单数字分频器在较宽频带上产生近乎完美的正交。PLL合成器内部产生2倍LO,所以不必在PCB周围分配,并且因为2倍LO架构只受LO信号沿而非频率成分影响,故在合成器和IQ调制器LO之间无需配置任何滤波器。

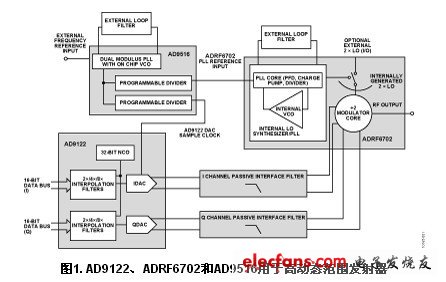

图 2. DAC输出频谱,蓝色实线表示基带信号和图像,红色虚线表示DAC正弦函数

信号采样至RF、总本底杂散

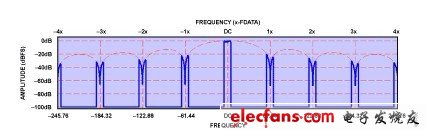

基带信号通过数个步进一直到达RF发射频率。该信号在离散(采样)域开始并由DAC合成至模拟域。这一步导致DAC产生图像和失真积。如图2所示,没有失真的理想DAC将会产生多幅基带信号图像,随后必须在调制前加以滤波。使用诸如AD9122系列的插值滤波器可以抑制大多数图像能量,但仍需要在DAC和调制器之间配置一个模拟接口滤波器。不过需要权衡取舍DAC插值和模拟滤波器的阶数。DAC插值速率越高,所需的模拟滤波器阶数越低,反之亦然。作为示例,图3显示了使用4倍插值时的DAC输出频率波形。

图3.使用4倍插值的DAC输出频谱,蓝色细线表示DAC插值转移函数

多种RF杂散分量并存

由于调制积、失真积和LO频率的整数倍,该信号链可能会大幅增加杂散分量。如果我们考虑所有讨论过的潜在杂散根源,杂散成分包括:

(j × LO_freq) + (k × DAC_sample_rate) +

(l × DAC_NCO_freq) + (m × DAC_input_IF)

其中j、k、I和m均为正无穷大和负无穷大之间的整数。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)