作者:施保华,金晓波,赵广州,秦娟英

由DSP(数字信号处理)芯片和FPGA(现场可编程逻辑门阵列)为核心组成的无线数字扩频通信平台是无线扩频通信的一个开放式平台,能用于无线接入、无线图象和音频传送、移动INTERNET、精确区域定位LPS、智能遥控探测等高科技领域。在此基础上增加液晶显示和触摸屏控制,从而能实现文字和图形信息的编辑和无线传送。

采用MicroTIps Technology Inc.公司的型号为MTG-32240X的中小规模液晶显示器(图形方式320*240点)。触摸屏控制器采用香港BURR-BROWN公司的ADS7843。我们对FPGA进行逻辑编程实现液晶显示控制器的功能。FPGA定时中断DSP(约占DSP工作时间的5%)来获取外部RAM的显示数据,然后,FPGA内部逻辑将显示数据送到液晶屏上进行显示。DSP对触摸屏的转换信号进行处理和计算以及完成各种文字和图形的编辑任务。即用DSP和FPGA一起来控制液晶的显示和文字、图形信息的编辑处理,并能接收触摸屏信号,从而实现笔输入掌上电脑的功能。再结合无线数字扩频通信平台就能实现文字和图形信息的无线传送。该产品能用于记者在通讯不便的现场进行文字和图形的实时编辑和采访报道以及在移动过程中需要进行文字和图形信息无线传送的地方。

MTG-32240X液晶模块特性

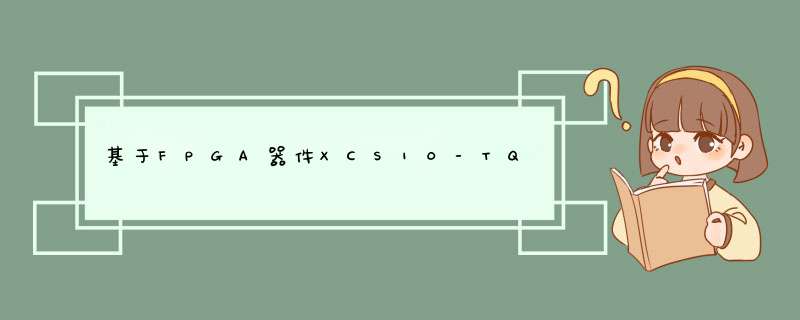

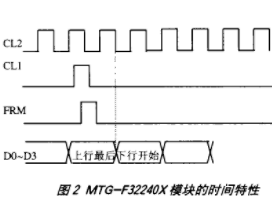

MTG-32240X是FSTN PosiTIve类、320*240象素、图形显示方式的液晶模块,它带有行列驱动电路以及EL背光电路,但是它没有微RAM(显示数据缓冲区),见图1。表1给出了液晶模块的引脚和功能说明。其中,CL2、CL1、FRM和D0"D3之间的时序配合如图3所示,CL2为1.28M Hz,CL1为16K Hz,FRM为66Hz。从图2和图3中可以看出,每行80个段移位脉冲(CL2) 后,发出一个换行信号(CL1);发出19200个段移位脉冲(CL2) 后,一帧(即240行)显示完成,发出帧开始信号(FRM)。以上过程不断重复,即可完成液晶屏的动态扫描显示。

FPGA的基本结构和功能

FPGA采用美国Xilinx公司性价比较高的XCS10-TQ144。现场可编程门阵列(FPGA)是80年代中期出现的一类新型用户可编程器件,与一般的可编程逻辑器件不同,FPGA的集成度高、逻辑实现能力强、设计灵活性更好。FPGA的基本结构通常包含三类可编程资源:可编程逻辑功能块(CLB)、可编程输入输出块和可编程互连。可编程逻辑功能块(CLB)是实现用户功能的基本单元,它们通常规则地排成一个阵列,散布于整个芯片;可编程输入输出块完成芯片上逻辑于外部封装腿的接口,常围绕着阵列排列于芯片四周;可编程内部互连包括各种长度的连接线段和一些可编程连接开关,它们将各个可编程逻辑块或输入输出块连接起来,构成特定功能的电路。

由于采用不同的开关元件,FPGA体现出不同的可编程特性,有些是一次性可编程的,另一些则是可重复编程的。一次性可编程的FPGA采用逆熔丝作开关元件,当在逆熔丝两端加上编程电压时,逆熔丝就会由高阻抗变为低阻抗,从而实现两个点间的连接。编程完毕后,即使撤除工作电压,这类FPGA的配置数据仍然保留。由于只能编程一次,因此它比较适合于定型产品及大批量应用。此外,它也常用于高性能及保密性要求高的场合。可重复编程的FPGA采用SRAM型开关或闪速EPROM控制的开关元件。SRAM型开关元件由一个用五个晶体管组成的RAM和一个叫做PIP(可编程内部连接点)的晶体管组成。PIP控制各个布线通道的连接,而PIP又由它们旁边的RAM单元控制。RAM单元中存储着PIP的通断信息,这些信息码是在系统上电时由外部写入到FPGA内部的RAM中的。电源切断后,RAM中的数据将会丟失,因此采用SRAM型开关的FPGA是易失性的,每次重新加电,FPGA都要重组。SRAM型FPGA的突出优点是可反复编程,系统上电时,给FPGA加载不同的配置数据,即可令其完成不同的硬件功能。这种配置的改变甚至可在系统运行中进行,实现系统功能的动态重构。

FPGA的逻辑设计要点

无线数字扩频通信平台中,DSP的主频为10.24MHz,用FPGA的逻辑八分频就能得到CL2的1.28MHz振荡频率,再用计数器分别对CL2脉冲进行计数就能得到CL1和FRM信号,计数值分别是80和19200。由于液晶模块上没有微RAM(显示缓冲区),因此在FPGA中构造两个32字的RAM,一个用于从DSP板上的RAM(64K字)读取显示数据,同时另一个用于将数据送到液晶屏上显示。从DSP板上读取显示数据时所用时钟频率为10.24MHz,用DSP的HOLD工作模式让DSP让出总线控制权。将数据送到液晶屏上显示时的频率为 1.28MHz。这样,FPGA将32字的显示数据送到液晶屏上显示需要100us,因此HOLD中断频率定为 100us。从而,可以分析出FPGA进行液晶显示控制将大约占用DSP工作时间的5%。考虑到不增加额外的硬件资源就能实现液晶显示控制,这样安排是比较合理的。通过FPGA的逻辑设计,FPGA也能发出读信号RD、片选信号DS和地址总线A0-A15,但这些信号只在HOLDA有效其间发出,其它时间为高阻态,从而FPGA不会影响DSP工作。

液晶显示触摸屏控制

通过以上设计,再结合电阻式触摸屏专用控制器ADS7843的应用就构成了集文字图形笔输入控制、编辑和无线传送于一体的无线掌上电脑产品。ADS7843是BURR-BROWN公司专用于4线电阻式触摸屏的12位模/数采样转换器,单一电源供电、完全降功耗模式、转换速度快。ADS7843大量用在电池供电PDA(personal digital assistants)和手持便携式装置中。通过DSP同步串行口对ADS7843进行接口控制就能获取触摸屏位置转换信号,再经DSP计算处理转化为待显示数据存入外部显示缓冲区,FPGA作为液晶显示控制器就能将显示缓冲区数据送到液晶屏上正确显示。同时,从触摸屏上得到的图形和经DSP编辑处理的各种信息也能通过无线扩频通信平台传送出去。当然,要完成上述功能还必须增加编辑软件和汉字库。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)