Aldec 多语言仿真器锁定主流用户

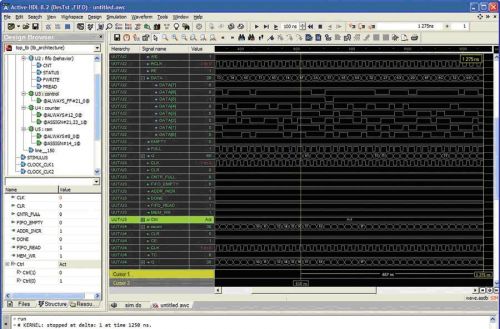

Aldec 公司日前推出了一款新型 AcTIve-HDL 多语言仿真器,定价为 1,995 美元,据称仿真速度是 FPGA 厂家提供的 RTL 仿真器的两倍。

据在内华达州亨德森市工作的公司营销副总裁 Dave Rinehart 称,FPGA 厂商提供的单语言仿真器的售价一般低于1,000 美元,第三方仿真工具厂商提供的单机版多语言仿真器起始价通常高于 6,000 美元,而 AcTIve-HDL Designer EdiTIon 的定价介于二者之间。

对当今的 FPGA 设计人员来说,在设计中混用 Verilog 和 VHDL IP 模块是一种常见的做法。实际上,部分设计人员,特别是近期才专注于 ASIC 的设计人员,甚至有机会采用 SystemVerilog 或 SystemC 等更高级的语言来开发或运用模块。

虽然有很多翻译器可以使用,但设计人员仍然需要使用仿真器,以便能够处理混合使用的几种最常见的语言。Aldec 的 AcTIve-HDL Designer Edition 支持 VHDL、Verilog 和 System Verilog 设计文件的混合语言仿真。此外,该工具还支持 VHDL与 Verilog 加密 IP 以及 Xilinx SecureIP,并对 FPGA 设计尺寸与性能没有限制。

Active-HDL Designer Edition 是 Aldec 的 Active-HDL 产品线的简化版本。Active-HDL 产品线运行速度要比 Active-HDL Designer Edition 快几倍,包含的功能也更为丰富,包括支持 SystemC、代码覆盖、设计规则检查、DSP 建模以及验证。Rinehart 表示,Aldec 在 Active-HDL Designer Edition 中添加了性能管理器,不过主流设计和验证工程师们可根据需要选择添加还是删除这些高端功能。滤除这些较为新颖的功能还可以减轻 Aldec 支持人员的工作负担,降低成本。

Rinehart 相信,许多设计人员会对 Designer Edition 产生深刻的印象,他们会升级到该工具的完整版本,充分享受其高级特性集带来的诸多好处。

单机版 (node-locked license) 和多机版 (floating license) 仿真器的定价分别为 1,995 美元和 2,495 美元,确实值得一试。如有意,敬请访问下列网址:www.aldec.com/DesignerEdition。

Aldec 推出的 Active-HDL Designer Edition 锁定厂商提供的单语言解决方案

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)