Cyclone II器件支持如SDR SDRAM,DDR SDRAM,DDR2 SDRAM以及QDRII RAM等外部存储器接口。下面将着重讨论Cyclone II器件如何实现DDR SDRAM接口控制的。

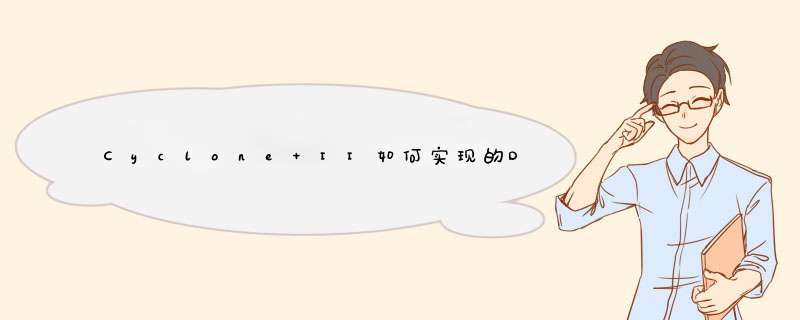

Cyclone II器件有专用的与DDR SDRAM接口的data(DQ),data strobe(DQS),clock管脚。一般是8个DQ信号对应与1个DQS信号,DQS信号和DQ信号从DDR SDRAM输出时是沿对齐的。进入FPGA后要想实现中心对齐,即DQS的变化沿与DQ的中心对齐,那么必须在FPGA内部对DQS做延时处理,如Figure 9-1所示。

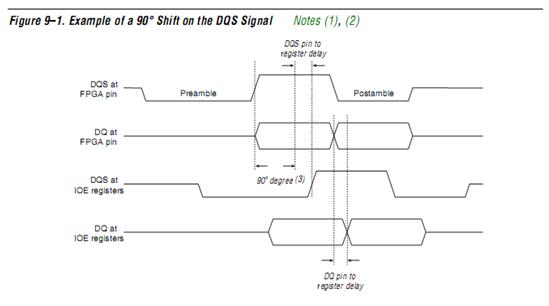

DDR输入接口实现如Figure 9-11所示。这也是一个涉及到异步时钟域数据通信的问题,且看它是如何进行同步的。resynch_clk是FPGA内部使用的时钟,DQS相对与和DQ同步的时钟。这两个时钟其实是同频不同相,相位偏移肯定是要满足FPGA的采样时钟和数据信号中心对齐,这涉及到DDR SDRAM的输出时钟信号的相位调整。

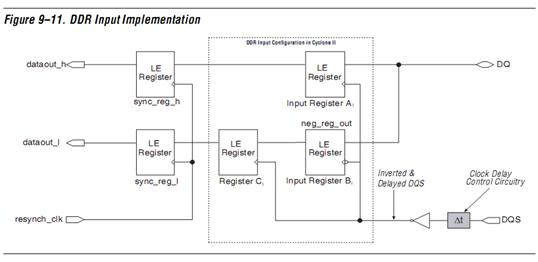

输入信号DQS经过反向延时后与DQ信号中心对齐,然后分别使用方向延时后的DQS信号的下降沿和上升沿锁存DQ信号前后输入的数据Q0和Q1,同时在上升沿时会对前一级采样的Q0信号再进行一次锁存,从而使Q0和Q1信号在被FPGA同步时钟采样前达到同频同相。FPGA内部时钟通过对经过处理后的Q0和Q1信号采样达到了双沿数据输入的采样。详细波形如Figure 9-12所示。

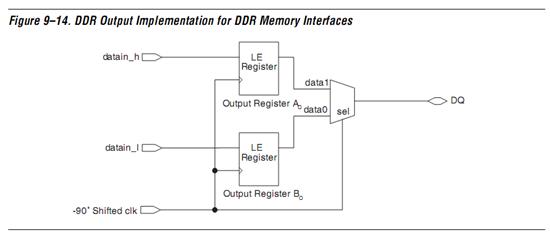

DDR输出接口实现如Figure 9-14所示。经过90度相移的DDR SDRAM时钟先对FPGA内部时钟域的待输出信号进行一次锁存,然后由相移时钟的高低电平选择作为当前输出给DDR SDRAM的数据信号。

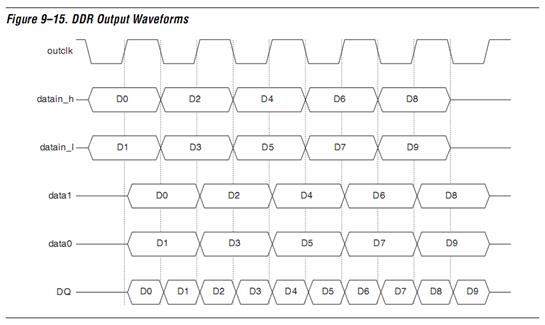

详细波形如Figure 9-15所示。

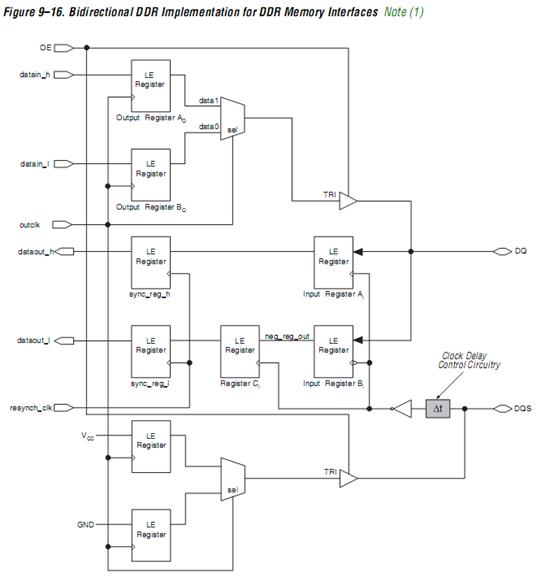

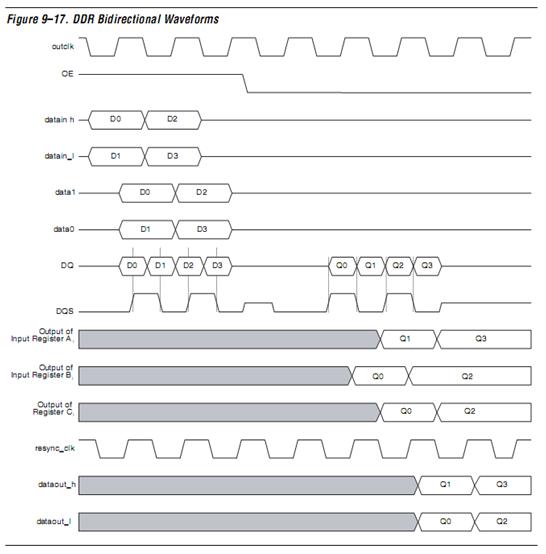

双向接口的实现只是将前面讨论的输入和输出方式进行综合。不论是DQ还是DQS信号,在作为FPGA的输入管脚时,内部给这个管脚的赋值为高阻态,从而确保读取的输入信号有效。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)