如何使用模拟滤波器注入噪声

例如,您 Δ-Σ ADC 输入端 RC 滤波器或放大器的低通滤波器会产生更大噪声的数字输出。难道您没有设计过降低噪声的滤波器来让您从转换器获得更多而非更少的无噪声位吗?通过一个模拟低通滤波器消除更高频率噪声,同将噪声注入到您滤波器截止频率以下的频带一样容易。如果您的滤波器在相关频带中产生噪声,那么相比您的预期,您的转换输出结果噪声会更大。

如果您通过减少您滤波器的电阻值来修改您的电路设计,那么您会增加电路的无噪声位。

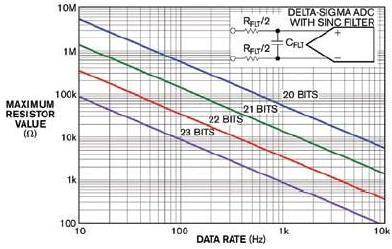

图1

例如,图 1 所示 Δ-Σ ADC 使用一个低通滤波器来降低转换器输出数据速率以上的噪声,即 FD。利用这种滤波器后,使用 Δ-Σ 转换器的输出数据速率来选择该电路的电阻和电容值。您可以使用公式 FD=1/(2πRFLT×CFLT),来计算 RFLT(滤波器电阻)和 CFLT(滤波器电容)的值。RFLT/2 和 CFLT 的组合开始生效时(请参见参考文献 1),该滤波器通过限定 (target) 转换器的采样频率来降低噪声。

该设计公式中缺少的细节是电阻噪声。不存在无噪电阻这样的东西。理想电阻噪声情况是:k 为波尔兹曼常数(1.38×10–23×JK–1),T 为开尔文温标 (Kelvin)温度,R 为 25°C 条件下欧姆单位的额定电阻,而 B 为以赫兹为单位的相关带宽。

现在,让我们来搞清楚电阻噪声公式是怎么一回事。您注入到您电路的噪声达到输出数据速率,其等于电阻噪声。要确定这种电路的最大允许电阻值,请使用下列方程式:

图 1 描述了该公式的特征,其中 ER 为 ADC 厂商产品说明书的规定有效精度。如果您在 200 Hz 数据速率下运行您的 23-bit 有效精度 Δ-Σ 转换器,则滤波器电阻的最大值为 4.297 kΩ 或者更低,而 RFLT/2 为 2.148 kΩ 或者更低。

作者简介

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)