在开始介绍 DDR 之前,首先要了解内存的功用为何。大多数的 3C 产品在运作时,会将正在使用的程式存放到一个短期数据储存区,该空间即为内存,所以有了内存的运用能使 3C 产品更快速的切换程序以方便使用。

内存的历史

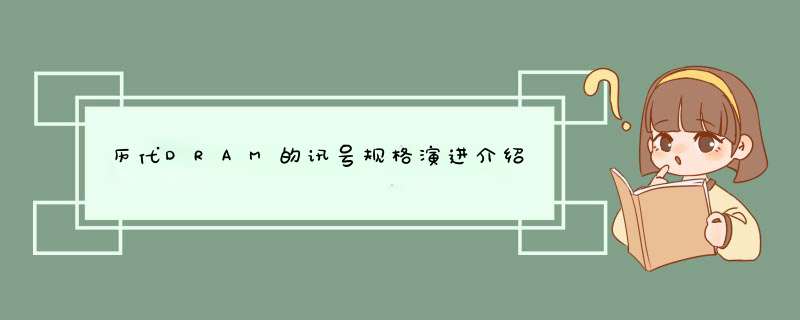

图一为内存的种类及发展史:

图一:内存的种类及发展史

内存(Memory)又可分为 DRAM(Dynamic Random Access Memory)动态随机存取内存和 SRAM (StaTIc Random Access Memory)静态随机存取内存两种。两种都是挥发性的内存,SRAM 的主要使用 flip-flop 正反器,通常用于快取 (Cache),而 DRAM 则是使用电容器及晶体管组成。RDRAM (Rambus DRAM)因较为少见也非本篇文章主角,其他还有早期的 FP RAM、EDO RAM 也就不多作介绍。

DRAM 中又以 SDRAM(Synchronous Dynamic Random Access Memory)同步动态随机存取内存在近几年来最广为使用,SDRAM 最重要的就是能够“同步”内存与处理器(CPU)的频率,让 SDRAM 频率可超过 100MHz 使传输数据更能实时到位。SDRAM 亦可称为 SDR SDRAM(Single Data Rate SDRAM)。

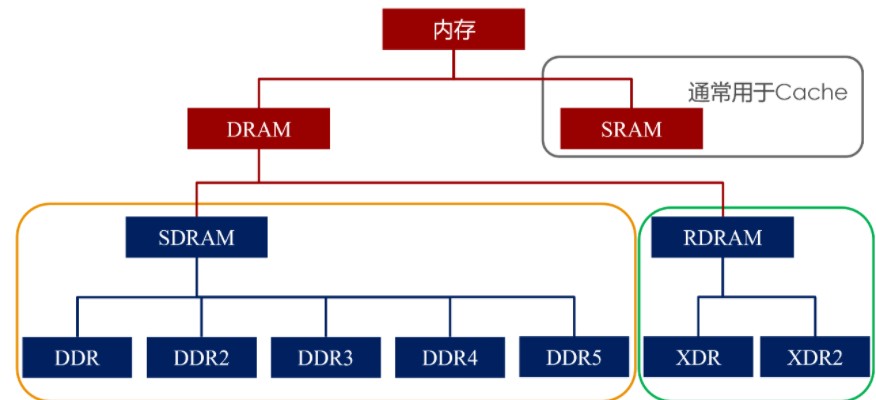

DDR(Double Data Rate)其实指的是 DDR SDRAM(Double Data Rate SDRAM),SDRAM 及 DDR 主要差异有三点整理如下:

目前负责订定 DDR 规范的协会为 JEDEC(Joint Electron Device Engineering Council),但现在它的全名则是 JEDEC 固态技术协会(JEDEC Solid State Technology AssociaTIon)。

DDR 历代规格介绍

有了内存的认识之后,这边将历代 DRAM 的规格整理如下:

历代演进除了传输速率越来越快还有工作电压越来越低,内存Topology在DDR2之前Command/Address和Clock用T-Branch分支方式传给每一个内存颗粒,但在DDR3之后 Command/Address和Clock则改用 Fly-by串列给每一个内存颗粒。

另外内存链接形式在 DDR3 之前采用处理器(CPU)同时与多个内存芯片控制器链接的“多重分支”,但在DDR4 之后每个内存芯片控制器有单独与 CPU 链接的通道,即为“点对点”的连结形式。

DDR 主要讯号介绍

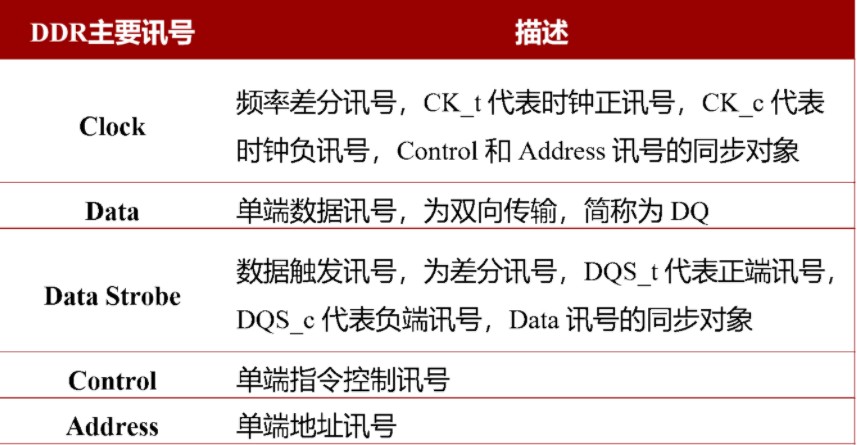

DDR 的讯号类型主要分为以下五种如下:

Note: 读取(Read)时,DQ 和 DQS 为同相位。写入(Write)时,DQ 和 DQS 会有 90 度的相位差。

责任编辑:pj

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)