1、差分时钟

差分时钟是DDR的一个非常重要的设计,是对触发时钟进行校准,主要原因是DDR数据的双沿采样。由于数据是在时钟的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就对CK的上下沿间距有了精确的控制的要求。一般说来,因为温度、电阻性能的改变等原因,CK上下沿间距可能发生变化,此时与其反相的CK#就起到纠正的作用,因为,CK上升沿快下降沿慢,CK#则是上升沿慢下降沿快。也就是,与CK反相的CK#保证了触发时机的准确性。

2、数据选取脉冲(DQS)

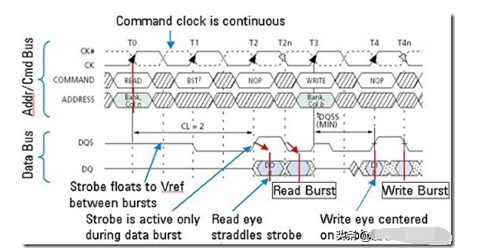

DQS是DDRSDRAM中的另一项关键技术,它的功能是用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。每一颗芯片都有一个DQS信号线,它是双向的,在写入时它用来传送由芯片发来的DQS信号,读取时,则由内存生成DQS向芯片发送。因此可以认为DQS就是数据的同步信号。

我们知道DDR之前的SDR就是使用clock来同步的,因此理论上,DQ的读写时序完全可以由clock来同步。但是,由于速度提高之后,可用的时序余量越来越小,而引入DQS是为了降低系统设计的难度和可靠性,也就是可以不用考虑DQ和clock之间的直接关系,只用分组考虑DQ和DQS之间的关系,很容易同组同层处理。

DQ和DQS只是组成了源同步时序的传输关系,可以保证数据在接收端被正确的锁存,但是IC工作时,内部真正的同步时钟是clock而不是DQS,数据要在IC内部传输存储同样需要和clock(内部时钟比外部时钟慢)去同步,所以就要求所有的DQ信号还是同步的,而且和clock保持一定的关系,所以就要控制DQS和clock之间的延时了。

在写入时,以DQS的高/低电平期中部为数据周期分割点,而不是上/下沿,但数据的接收触发仍为DQS的上/下沿。

3、延迟锁定回路(DLL)

第三个关键技术是DLL技术,也就是延迟锁定回路。需要这种技术的原因是,内外时钟的不同步问题。内外时钟不同步在SDRAM中就存在了,不过因为它的工作/传输频率较低,所以内外同步问题并不突出。但是,DDRSDRAM对时钟的精确性有着很高的要求,而DDRSDRAM有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟,在理论上DDRSDRAM这两个时钟应该是同步的,但由于种种原因,比如温度、电压波动而产生延迟使两者很难同步,更何况时钟频率本身也有不稳定的情况。我们熟悉的DDRSDRAM的tAC就是因为内部时钟与外部时钟有偏差而引起的,它很可能造成因数据不同步而产生错误。

怎么解决呢?实际上,因为不同步就是一种正/负延迟,如果延迟不可避免,那么若是设定一个延迟值,如一个时钟周期,那么内外时钟的上升与下降沿还是同步的。鉴于外部时钟周期也不会绝对统一,所以需要根据外部时钟动态修正内部时钟的延迟来实现与外部时钟的同步,这就是DLL的任务。

DLL主要的目的就是生成一个延迟量给内部时钟,来补充正负不同步造成的正负延迟。

有了这些技术就构成了内存帝国的最基本的元素,之后的DDR2,DDR3和DDR4以及最新的DDR5将以此为基础,内存的功耗及频率得到一次又一次的飞跃。

责任编辑人:CC

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)