经历了几年的高速发展之后,人工智能(简称AI)不再是新鲜的名词,它已经作为一个重要的生产工具,被引入到我们工作和生活的多个领域。但在AI爆发的背后,随之而来的是对AI算力需求的暴增。

据OpenAI的一份报告显示,从2012年到2019年,人工智能训练集增长了30万倍,每3.43个月翻一番,但如果是以摩尔定律的速度,只会有 12 倍的增长。为了满足AI算力的需求,从业人员通过设计专用的AI芯片、重配置硬件和算法创新等多方面入手来达成目标。

AI算力需求增长

然而在此过程中,我们除了看到AI对算力的要求以外,内存带宽也是限制AI芯片发展的另一个关键要素。这就需要从传统的冯诺依曼架构谈起。作为当前芯片的主流架构,冯诺依曼架构的一大特征就是计算和内存分离的。那就意味着每进行一次计算,计算单元都要从内存中读取数据然后计算,再把计算结构存回到内存当中。

经典的冯诺依曼架构

在过往,这个架构的短板并不是很明显,因为处理器和内存的速度都都非常接近。但众所周知的是,在摩尔定律指导下的处理器在过去几十年里发生了翻天覆地的变化,但常用的DRAM方案与之相比,提升幅度不值一提。

再者,在AI时代,数据传输量越来越大。先进的驾驶员辅助系统(ADAS)为例。第3级及更高级别系统的复杂数据处理需要超过200 GB/s的内存带宽。这些高带宽是复杂的AI/ML算法的基本需求,在道路上自驾过程中这些算法需要快速执行大量计算并安全地执行实时决策。在第5级,即完全自主驾驶,车辆能够独立地对交通标志和信号的动态环境作出反应,以及准确地预测汽车、卡车、自行车和行人的移动,将需要巨大的内存带宽。

因此,AI芯片寻找新的内存方案迫在眉睫,其中HBM和GDDR SDRAM(简称GDDR)就成为了行业的选择。

为什么是HBM和GDDR ?

HBM就是High Bandwidth Memory的缩写,也就是高带宽内存,这是一项在2013年10月被JEDEC采纳为业界标准的内存技术。按照AMD的介绍,这种新型的 CPU/GPU 内存芯片(即 “RAM”),就像摩天大厦中的楼层一样可以垂直堆叠。基于这种设计,信息交换的时间将会缩短。这些堆叠的芯片通过称为“中介层 (Interposer)”的超快速互联方式连接至 CPU 或 GPU。将HBM的堆栈插入到中介层中,放置于 CPU 或 GPU 旁边,然后将组装后的模块连接至电路板。

尽管这些 HBM 堆栈没有以物理方式与 CPU 或 GPU 集成,但通过中介层紧凑而快速地连接后,HBM 具备的特性几乎和芯片集成的 RAM 一样。更重要的是,这些独特的设计能给

开发者带来功耗、性能和尺寸等多个方面的优势。

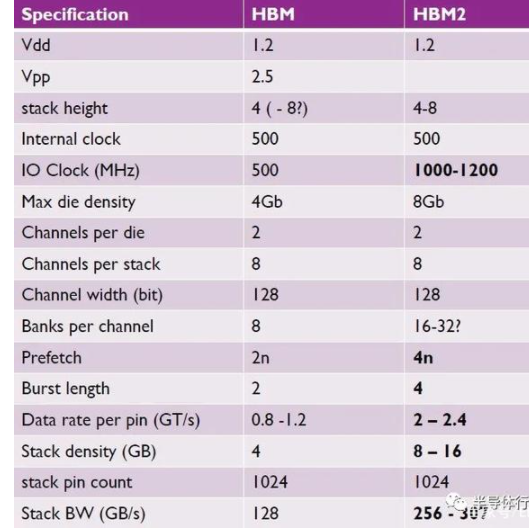

从第一代HBM与2013年面世后,JEDEC又分别在2016年和2018把HBM2和HBM2E纳为行业标准。据了解,在HBM2E规范下,当传输速率上升到每管脚3.6Gbps时,HBM2E可以实现每堆栈461GB/s的内存带宽。此外,HBM2E支持12个DRAM的堆栈,内存容量高达每堆栈24 GB。

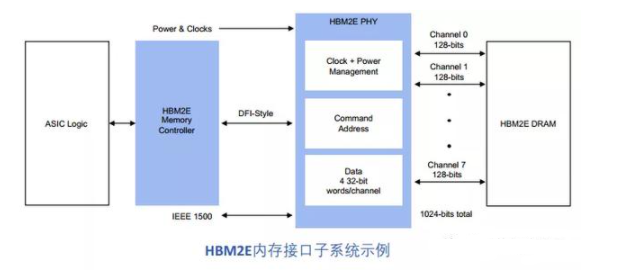

具体而言,就是说每一个运行速度高达3.6Gbps的HBM2E堆栈通过1024个数据“线”的接口连接到它的相关处理器。通过命令和地址,线的数量增加到大约1700条。这远远超出了标准PCB所能支持的范围。因此,硅中介层被采用作为连接内存堆栈和处理器的中介。与SoC一样,精细数据走线可以在硅中介层中以蚀刻间隔的方式实现,以获得HBM接口所需数量的数据线数。

得益于其巨大内存带宽的能力,使得连接到一个处理器的四块HBM2E内存堆栈将提供超过1.8 TB/s的带宽。通过3D堆叠内存,可以以极小的空间实现高带宽和高容量需求。进一步,通过保持相对较低的数据传输速率,并使内存靠近处理器,总体系统功率得以维持在较低水位。

根据Rambus的介绍,HBM2E的性能非常出色,所增加的采用和制造成本可以透过节省的电路板空间和电力相互的缓解 。在物理空间日益受限的数据中心环境中,HBM2E紧凑的体系结构提供了切实的好处。它的低功率意味着它的热负荷较低,在这种环境中,冷却成本通常是几个最大的运营成本之一。

正因为如此,HBM2E成为了AI芯片的一个优先选择,这也是英伟达在Tesla A100和谷歌在二代TPU上选择这个内存方案的原因。但如前面所说,因为HBM独特的设计,其复杂性、成本都高于其他方案,这时候,GDDR就发挥了重大的作用。

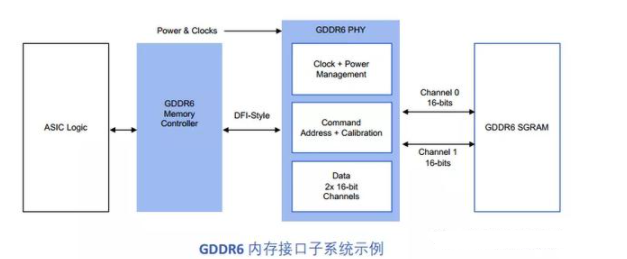

据了解,图形DDR SDRAM(GDDR SDRAM)最初是20多年前为游戏和显卡市场设计的。在这段时间内,GDDR经历了几次重大变革,最新一代GDDR6的数据传输速率为16Gbps。GDDR6提供了令人印象深刻的带宽、容量、延迟和功率。它将工作电压从1.5V降低到1.35V以获得更高的功率效率,并使GDDR5内存的数据传输速率(16比8 Gbps)和容量(16比8 GB)翻了一番。Rambus已经演示了一个运行速度为18 Gbps的GDDR6接口,显示这种内存架构还有额外的增长空间。

与HBM2E不同,GDDR6 DRAM采用与生产标准DDR式DRAM的大批量制造和组装一样的技术。更具体地说,GDDR6采用传统的方法,通过标准PCB将封装和测试的DRAMs与SoC连接在一起。利用现有的基础架构和流程为系统设计者提供了熟悉度,从而降低了成本和实现的复杂性。

与HBM2E宽而慢的内存接口不同,GDDR6接口窄而快。两个16位宽通道(32条数据线)将GDDR6 PHY连接到相关的SDRAM。GDDR6接口以每针16 Gbps的速度运行,可以提供64 GB/s的带宽。回到我们之前的L3汽车示例,GDDR6内存系统以连接四个DRAM设备为例,带宽可以达到200 GB/s。

采用GDDR6的主要设计挑战也来自于它最强大的特性之一:速度。在较低的电压条件,16 Gbps的信号速度下,保持信号完整性需要大量的专业经验知识。设计人员面临更紧的时序和电压裕度量损失,这些损失来源与影响都在迅速增加。系统的接口行为、封装和电路板需要相互影响,需要采用协同设计方法来保证系统的信号完整性。

总的来说,GDDR6内存的优异性能特性建立久经考验的基础制造过程之上,是人工智能推理的理想内存解决方案。其出色的性价比使其适合在广泛的边缘网络和物联网终端设备上大量采用。

Rambus将扮演重要角色

从上文的介绍中,我们看到了HBM2E和GDDR 6在AI中的重要作用,而要真正将其落实到AI芯片中,相应的IP供应商将是很关键的一环,而Rambus将扮演这个重要角色。

据Rambus大中华区总经理Raymond Su介绍,Rambus成立于上个世纪90年代,是一家领先的Silicon IP和芯片提供商,公司主要致力于让数据传输得更快、更安全。而从产品上看,Rambus的产品主要聚焦于三大块:分别是基础架构许可、Silicon IP授权,还有buffer chip芯片业务。

“得益于这些深厚的积累,我们能提供友商所不具备的差异性服务”,Raymond Su补充说。他指出:

首先,在内存IP层面,Rambus提供一站式的采购和“turn key”服务。而公司在去年完成的对全球知名的IP控制器公司Northwest Logic和对Verimatrix安全IP业务部,可以让Rambus能够提供更好的一站式的服务。

“通过这样的服务,Rambus IP可以很好地帮助客户尽早地把产品推向市场”,Raymond Su表示。

其次,作为全球领先的HBM IP供应商,Rambus在全球已经有50多个成功项目案例,积累了大量的经验;而在DDR5 Buffer Chip(缓冲芯片)方面,Rambus也是全球首发。这让他们在DDR5时代有信心改变整个市场。而在AI芯片迫切需要的HBM2E和GDDR 6 IP方面,Rambus也都做好了准备。

从Rambus IP核产品营销高级总监Frank Ferro的介绍我们得知,他们将HBM2E的性能提升到了4Gbps。在他看来,这个速度是一个全新的行业标杆,而此次Rambus发布我们全新的HBM2E产品也正是实现了这一行业最高标准。

根据Rambus发布的白皮书介绍,他们HBM2E接口完全符合JEDEC JESD235B标准。支持每个数据引脚高达3.6 Gbps的数据传输速率。该接口具有8个独立的通道,每个通道包含128位,总数据宽度为1024位。由此每个堆栈支持的带宽是461GB/s,每个堆栈由2、4、8或12个DRAMs组成。

作为一个为2.5D系统设计的IP,它有一个用于在3D-DRAM堆栈和SoC上的PHY之间的中介层由提供信号绕线。这种信号密度和堆积尺寸的组合需要特殊的设计考虑。为了便于实施和提高了设计的灵活性,Rambus对整个2.5D系统进行完整的信号和功率完整性分析,以确保所有信号、功率和散热要求都得到满足。而在于其他竞争对手相比,Rambus的HBM IP则有着大多数厂商布局的几点核心优势:

第一,Rambus提供的是完全集成而且经过验证的PHY以及内存控制器IP解决方案,在物理层面实现完整的集成互联。除了完整的内存子系统之外,他们的PHY也经过了硬核化处理,同时也完成了TIming closed也就是时序收敛的工作。

“我们给客户提供的并不仅仅是自己的IP授权、IP产品,我们也会向客户提供系统级的全面的集成支持,以及相关的工具套件,以及我们的技术服务。同时,我们也可以帮助客户更加进一步地减少设计实现的难度。” Frank Ferro补充说。他进一步指出,在发布了这个IP之后,Rambus将会为人工智能以及机器学习的应用客户提供更加完整的解决方案,帮助他们进一步地提高带宽,满足他们在带宽上的需求。

第二,Rambus拥有非常强大的HBM生产经验,在这方面,公司已经拥有了全球超过50家成功的客户案例,这在全球是名列前茅的。更重要的一点,Rambus所有合作客户的芯片从设计到原型再到投产,并不需要任何的设计返工,基本上所有的芯片都会实现一次的成功。这足以体现他们的实力。

第三,Rambus为客户提供非常完整的参考设计框架,其中最重要的一点就是如何更好地对中介层进行完整的设计和表征化的处理。“因为对于中介层来,讲它是PHY层和DRAM层之间沟通的重要环节,在这个过程中,因为速度非常快,所以说如何保证信号完整性也是必须要去考虑的。” Frank Ferro表示。

他进一步指出,Rambus与客户非常紧密地进行合作,并为他们提供非常完整的参考设计框架,然后帮助他们更好地去设计自己的中介层以及产品的封装。除此之外,Rambus也帮助客户做仿真分析,让他们对自己每个信号的通道进行完整的分析,来实现整个产品的最高性能。

第四,这也是非常重要的一点,那就是Rambus有一套非常重要的工具——Lab StaTIon。借助这个工具,Rambus会与客户进行合作,让他们将其HBM2E解决方案直接插入到他们的终端系统当中,来构建一个非常独立的内存子系统。

能在HBM2E IP获得这样的成就,一方面,Rambus的研发投入功不可没;另一方面,他们与SK海力士、AIChip和台积电多方人员的通力合作,也是他们能提供快速服务的原因之一。例如在SK海力士方面,它为Rambus提供的HBM2E内存达到了3.6G的数据传输速率,而在和合作过程中,两者又将HBM2E的速率进一步地推进到了4.0 Gbps;AIchip则为Rambus提供了ASIC的相关解决方案以及产品,帮助其设计了相关中介层以及封装;此外,台积电提供了一个交钥匙的2.5D Cowos封装以及解决方案,来更好地为Rambus打造一个晶圆上的基本架构。

“我们的解决方案适用于人工智能以及机器学习的训练,同时也非常适用于高性能计算系统和5G网络的基础设施建设”,Frank Ferro最后说。

除了面向AI训练的HMB2E IP,Rambus还推出了面向AI推理的GDDR 6产品。

据Rambus的白皮书介绍,公司的GDDR6接口专为性能和功率效率而设计,支持AI/ML和ADAS推理高带宽与低延迟要求。它由一个经共同验证的PHY和数字控制器组成,提供一个完整的GDDR6内存子系统。Rambus GDDR6接口完全符合JEDEC GDDR6 JESD250标准,每个引脚支持高达16 Gbps。GDDR6接口支持2个通道,每个通道有16位,

总数据宽度为32位。Rambus GDDR6接口每针16 Gbps,提供带宽为64 GB/s。

通过直接与客户合作,Rambus能提供完整的系统信号和电源完整性(SI/PI)分析,创建优化的芯片布线版图。客户收到一个硬核解决方案与全套测试软件可以快速启动,定性和调试。

在“内存墙”的限制下,为了满足AI应用的数据搬运需求,产业界正在探索不同的方法来解决问题。例如英国AI芯片初创企业Graphcore就希望通过分布式内存设计的方法解决这个问题。

而Rambus的这两个方案出现那就给开发者们提供了在传统架构设计上获得性能大提升的可能。

编辑:hfy

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)