自从2004年PCI-E 1.0a规范之后,主板上就开始有了最新的串行高速PCI-E总线,相比原来的PCI V2.3,PCI-E总线有很大的优势,首先,PCI-E降低了芯片连接的管脚数量,简化了PCB板的设计和布局;其次,PCI-E是非共享的串行差分接口,不会出现多个设备共享带宽的情况,PCI-E x1的理论带宽为发送、接收各250M字节/秒,PCI-E x4的理论带宽为发送、接收各1G字节/秒,并且在PCI-E 2.0 协议中会使用5G BPS的更高速的物理层收发器,速度会翻倍。因此,PCI-E总线接口特别适合于超高速的数据传送,并且会在3年之内完成对PCI接口的替代。我公司根据这一情况,为满足市场需要,特推出S2300型PCI-E接口FPGA开发实验平台,满足用户对高速数据传送的需求。

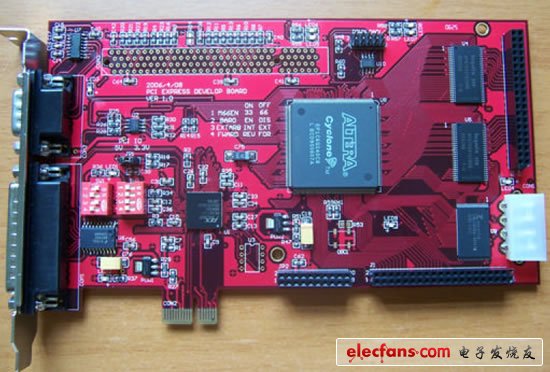

该开发实验板采用 PCI -E x1 接口,为方便用户进行自主开发,提供了 80 个可用的 FPGA IO 输入输出,用户可以自行设计应用接插板,如外部 A/D 数据采集,图象数据处理等系统应用,而不需要对 PCI -E 接口有过多的了解。

PCI-E 接口芯片采用了 PLX 公司的 PLX8111BB66BC ,完全支持 PCI -E 1.0A 协议,外部接口最高支持 66M 的工作频率, 32 位总线的宽度,支持最大 266M 字节 / 秒的突发峰值传送速度。

核心FPGA芯片采用 ALTERA 公司的新型 CYCLONE FPGA 系列, EP1C12Q240C8, 容量分别为 12000 个逻辑宏单元,等效于标准 30 万逻辑门电路,速度为 -8 ,编译后系统速度可以达到 100MHz ,可以支持 ALTERA 公司的 SOPC 内核 NIOS2 系统的开发, NIOS2 开发环境编译后的可执行文件可以通过 PCI 接口下载到开发板上的 FLASH 中去。

PCI-E 开发板照片

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)