1 引言

生物电信号是由生物体发出的不稳定的微弱电信号,主要包括心电、肌电、脑电信号,其特点表现为信号弱、干扰强、精度高。因此,在生物体的多参数测量中,高精度尤为重要,这对信号采集速率、实时性和准确性等提出更高要求。

根据生物电信号特点,介绍一种基于Ez-USB FX2接口的生物电信号数据采集系统,它将传统医学仪器的优点与计算机强大的数据存储能力以及良好的人机界面相结合,符合医学仪器数字化、模块化、小型化的发展趋势,具有很好的应用前景。

2 EZ-USB FX2接口简介

高速设备通常具有支持高速传输的USB控制器以实现高速传输,选用内置增强型微处理器8051、可动态加载固件的USB2.0控制器EZ-USB FX2(CY7C68013),该器件相对于其他USB控制器,功能强大,开发难度较小且性价比较高。

2.1 基本特性

EZ-USB FX2功能强大,既负责USB事务处理,也兼具微处理器的控制功能,可用作USB外设主控器件。该器件集USB2.0收发器、串行接口引擎、增强型 8051、I2C总线以及通用可编程接口于一体,体积小巧,性价比高,广泛应用于存储器、打印机、扫描仪等各种USB外设。

2.2 端点缓存

USB规范定义端点作为发送数据的起始点或接收数据的目的地址。EZ-USB FX2包含3个64 B的端点缓冲区和4 KB的可配置端点缓冲区。其中3个64 B的缓冲区分别用于EP0,EPlIN和EP1OUT,而4 KB的可配置缓冲区用于EP2,EP4,EP6和EP8。端点0默认为控制端点,支持OUT和IN双向传输;端点1支持批量、中断和同步传输;而端点2、 4、6和8则是高带宽的数据传输端点,可配置成不同方式以适应不同带宽要求。

2.3 GPIF接口

EZ-USB FX2系列器件提供3种可用接口模式:端口模式、从属FIFO模式和GPIF主控制模式。端口模式下,所有I/O引脚都可作为8051的通用I/O接口;从属FIFO模式下,外部逻辑或外部处理器直接与EZ-USB FX2的端点FIFO相连,外部设备作为控制器,像普通FIFO一样对EZ-USB FX2中的端点数据缓冲区进行读写;而GPIF模式是一种内部主机控制模式,使用内部集成的高效控制逻辑取代外部微控制器来控制Ez-USB FX2端点FIFO。在EZ-USB FX2内部,GPIF内核就是一个可编程的状态机。

EZ-USB FX2使用4个用户定义的波形描述符控制状态机.从而实现FIFO以及单字节数据的读写 *** 作。每个GPIF波形描述符都由7段组成:S0~S6。执行完 S0~S6的动作后,进入idle状态(S7)即空闲状态,以准备启动下一次GPIF动作。每个state可定义为无判断不转移态(NDP)或判断转移态 (DP)。当某个state定义为NDP时,这个state动作的执行只是简单延时,用于确定产生指定电平的延续时间;当定义为DP时,它将根据 RDY0~RDY5上的输入信号状态,以及内部FIFO的可编程标志和内部自定义的Ready标志,将这些信号进行逻辑“与”、“或”、“异或”运算,并根据得到的逻辑结果在S0~S6中选择一个即将执行的state。执行每个state时,都可指定CTL0~CTL5输出用户指定的状态。通过RDYx和 CTLx以及内部一些标志位的组合,即能完成各种复杂时序电路的控制。由于GPIF接口的配置灵活,使得FX2可方便地和其他逻辑微处理器(例如单片机、 DSP、CPLD和FPGA等)进行数据的主动读写,这样便大大扩展GPIF模式的使用范围。GPIF模式下,8051可不参与数据传输,以突破高速、全速下的传输模式进一步接近EZ-USB FX2的传输带宽480 Mb/s。同时根据生物电信号的频率特征,将每个通道最大采样频率设为100 kHz,在GPIF接口模式下完全能够满足系统要求。

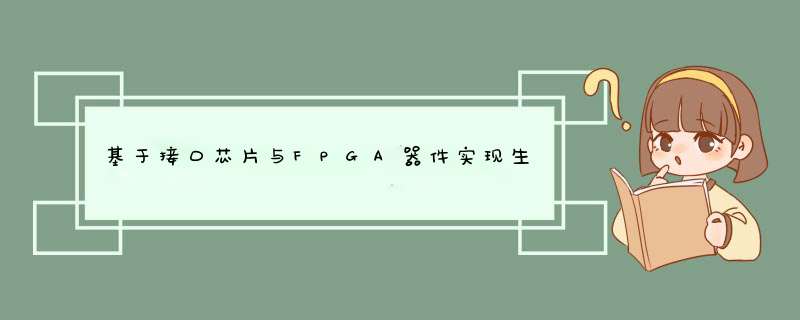

3 系统结构

系统结构框架如图1所示。通过导联由人体采集到的心电、脑电、肌电等信号调理电路后,由FPGA内部逻辑控制A/D转换对其采样。将经采样并通过A/D转换后的数据暂时缓存到EZ-USB FX2的内部FIFO中,供PC机读取。整个系统涉及A/D转换及其通道选择、信号放大、FPGA控制和EZ-USBFX2接口设计,这里主要介绍EZ- USB FX2接口设计,以及相应固件程序的开发与GPIF波形设计。

4 器件资源分配

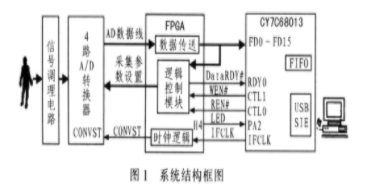

4.1 EZ-USB FX2与FPGA的硬件连接

EZ-USB FX2采用GPIF接口和FPGA相连,其硬件连接电路如图2所示。EZ-USB FX2与FPGA连接的引脚分配如下:FD0~FD15为GPIF双向数据线,负责读写数据:CTL0、CTL1分别为读(REN#)、写(WEN#)使能信号;RDY0为FPGA发出的数据准备好信号;PA2与FPGA的H4引脚连接,用于数据采集开始时点亮LED。

4.2 端点分配

系统中数据通道分为数据上传通道以及配置和控制命令通道,根据设计需要,选择其中两个端点分别作为发送和接收端点。配置如下:EP2用于从USB向FPGA传输采集控制命令,4×512字节缓冲,传输类型为批量OUT传输方式;EP6用于从 FPGA向USB传输数据采集结果,4×512字节缓冲,传输类型为批量IN传输方式。EZ-USB FX2相当于一个中转站,一方面将FPGA发来的采集数据传输给主机,另一方面将主机发送的数据采集参数传输至FPGA,便于控制A/D转换。

5 固件程序设计

固件是设备运行的核心,其主要功能是控制EZ-USB FX2处理驱动程序请求(如请求设备描述符、请求或设置设备状态及设备接口等USB2.0标准请求)、向FPGA发送采集参数、通过EZ-USB FX2缓存数据并实时上传至PC等。

本系统中,即使使用外部逻辑和内置通用可编程接口,在没有CPU的干涉下能够通过4个端点FIFO处理高速带宽数据,固件还需器件初始化、GPIF波形初始化、控制和监测GPIF的动作。

5.1 器件初始化

同件初始化函数为TD_Init(),主要负责对EZ-USB FX2的初始化,在同件开始运行时调用该甬数。其初始化工作主要分为以下步骤:

(1)设置EZ-USB FX2的IFCLK输出频率,将时钟频率设置为内部时钟48 MHz;

(2)设置EZ-USB FX2的EP2为BULK、OUT传输方式,EP6为BULK、IN传输方式,均为4倍缓冲;

(3)复位EP2 FIFO并设置为Auto OUT模式,复位EP6FIFO并设置为Auto IN模式;

(4)调用GpifInit()函数,初始化GPIF所需的寄存器;对EP2OUT、GPIF使用EF标志,对EP6IN,GPIF使用FF标志;

(5)初始化PA2为输出引脚并置为低电平,高电平时点亮LED。

5.2 GPIF波形设计

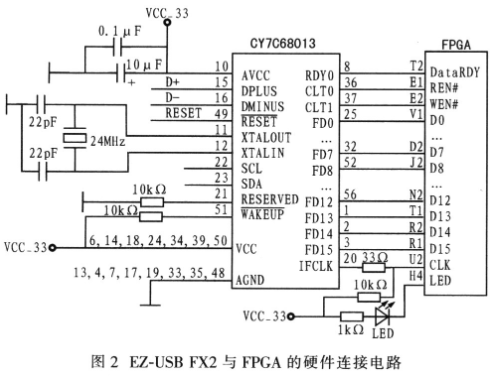

EZ-USB FX2固件程序可指定某个波形为4个端点中的任意一个工作,GPIF将在接口产生使能信号和握手信号,将数据送入或送出端点FIFO。在本系统中,对 FPGA写命令时则通过FIFO Write实现;读取所采集到的数据时,则通过FI-FO Read实现。波形设计如下:

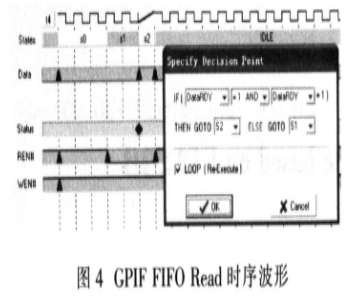

(1)图3为FIFO Write时序波形,用于向FPGA发送采集控制参数。S0为非活动状态,当WEN#置低时跳入S1状态,S2设为Next FIFO Data,依次将数据写入FPGA的寄存器中。

(2)图4为FIFO Read时序波形,它描述了采集数据的读传输,S0为非活动状态,S1为读 *** 作的引导状态并将REN#置低。当接收到FPGA发送的DataRDY=1 后,跳入S2。将S2设为FlowState,逻辑控制数据从FPGA中读出并 *** 作REN#的状态,即当Tcxpire=1时,将REN#置高,跳入 IDIE状态。在FlowState状态下,WEN#置高,写使能关闭。

5.3 数据采集流程

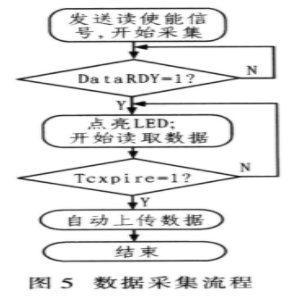

程序开始,主函数调用TD_Init()和Gpiflnit()函数,初始化寄存器,并通过2个自动指针寄存器AUTOPTR1和AU-TOPTR2,把生成的GPIF波形程序调入器件的RAM,然后状态机开始运行,产生所设计的控制波形。采集参数下传后,FPGA解析参数,延时,EZ-USB FX2向FPGA发送读使能信号,开始采集数据,数据采集程序流程如图5所示。如果FP-GA返回DataRDY=1,在TD_Poll()函数中执行读取数据传输程序。完成该过程后,程序根据主机请求,开始自动上传数据。

6 结束语

基于FPGA控制电路、EZ-USB FX2高速传输的数据采集系统,可同时采集16位生物电信号;EZ-USB FX2采用GPIF接口模式,8051可不参与数据传输,以突破高速、全速下的传输模式,解决了外围设备和EZ-USB FX2接口之间存在的传输瓶颈问题:同时A/D转换脱离了EZ-USB FX2,而由FPGA完全控制,避免了直接上传时的数据丢失。该系统设计具有结构简单、数据不丢失且传输速率高等优点,因此在生物电信号数据采集中具有良好的实用价值和应用前景。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)