正电子发射断层成像(PET)是核医学领域一项先进的临床造影检查技术,它通过向人体内注入放射性示踪剂,基于生物体的新陈代谢,从细胞和分子水平提供人体功能性病变信息,作为高性能的无创检测手段,以其灵敏度高、特异性好、全身显像、安全性高的优点,在疾病(特别是肿瘤、心脏、神经系统等)的诊断、治疗、疗效评价、基础医学研究等方面发挥着重要作用。近些年来,基于飞行时间技术的TOF-PET更是成为了研究的热点,与传统的PET相比,TOF技术的引用能够显着提高输出图像的信噪比和对疾病的诊断精度。

从PET系统整体发展历程来看,外形变化微小,但其核心技术包括晶体、光电倍增管、前端电子系统、校正技术、重建算法等均发生了革命性的飞跃。技术与方法的突破旨在不断提高的空间/时间分辨率、灵敏度及输出图像的质量。前端电子系统是连接探测器与图像输出的桥梁,其设计直接影响着系统的整体探测性能。本文从前端电子系统采集的角度出发,以优化现有系统的时间分辨性能与能量分辨性能为目的,分析系统对TOF时间分辨性能降级的因素,并对其进行优化与测试。

1PET采集系统

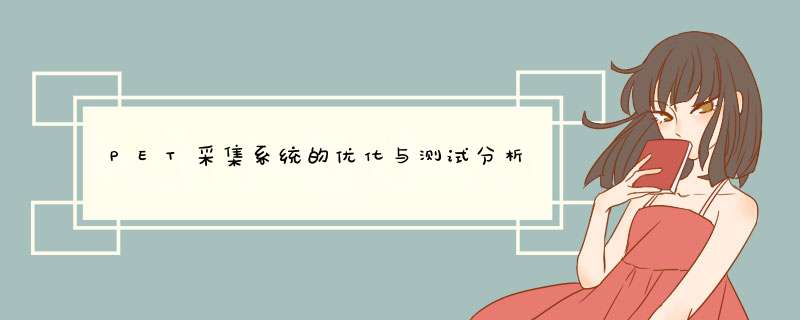

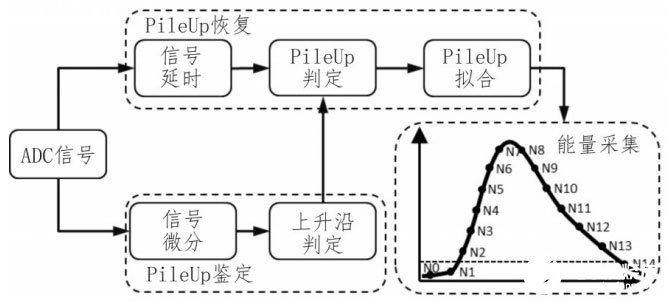

PET系统的时间/空间分辨能力、灵敏度等主要是由PET成像系统的探测器模组及其前端电子系统决定。其中PET系统中数据采集和处理部分的主要功能是将光电倍增管探测到的光信号转换为电信号,然后由两大链路分别进行处理,一是时间链路,与符合时间窗相互结合用于确定光子发生湮灭点的位置;另一个是能量链路,用来确定被光子击中晶体的位置,即响应线LOR的具体位置,两者结合实现对湮灭事件点的空间定位,系统流程图如图1所示。

图1TOF-PET系统电子端流程图

通过分析可知,PET系统对前端电子系统设计的具体要求为:

1)同步时钟的一致性及稳定性;

2)能量链路的PileUp堆积处理及快速采集;

3)时间链路上升沿的陡峭性及鉴相器的定时准确性;

4)时间数字转换TDC模块的测量精度;

其中系统全局时钟的同步、能量链路的快速采集及时间链路的测量一直是研究的热点与难点。

2全局时钟

在基于TOF技术的PET系统中,为了能够精准地获得各个光子到达探测器的时间,从而要求对多个探测模块的数据能够有一个统一的时间基准,全局时钟信号的稳定性与精度直接影响PET系统的检测质量。在全局时钟的设计中,一般采用一个时钟扇出源对多个时钟节点的电路板进行时钟信号发送,时钟节点以接收到的时钟作为本地时钟,但是当该时钟信号噪声较大时,时钟抖动产生的频率与相位误差无法满足系统时钟的设计需求,为了解决这一问题,本文采用抖动滤除器件对输入时钟信号的抖动进行噪声滤除,实现与时钟频率同步且低抖动信号的输出。

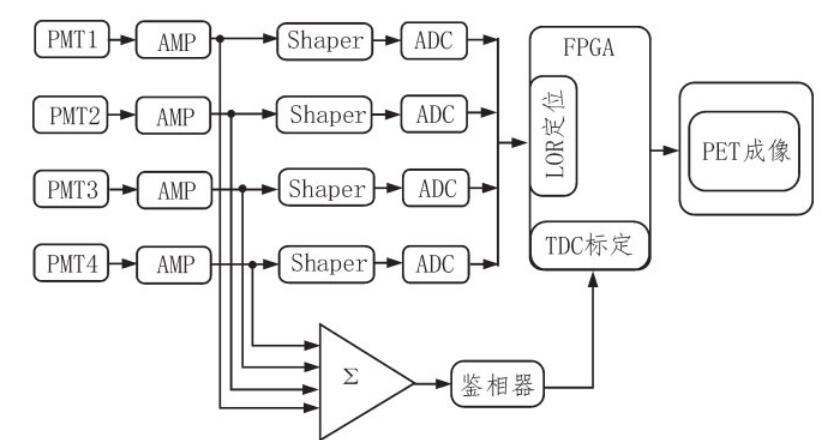

系统采用星形拓扑结构,利用同轴电缆互联,如图2所示,以Block0作为时钟参考节点,对每个模块进行时钟扇出,通过J01~J03输出时钟信号和同步信号,J01对应两个信号模式,其余模块通过J04clock接口接收全局时钟信号和同步信号。LMK04906具有3个输入口,通过各个模块J05和时钟参考节点block0进行数据通信。

图2低抖动时钟同步方案

设计中每个模块均采用时钟抖动消除芯片LMK04906进行时钟去抖,其中,LMK04906的第一级锁相环实现抖动滤除功能,实现输出时钟具有低抖动的近端噪声,第二级锁相环利用内部集成的高性能LC振荡器实现时钟倍频,实现超低抖动的远端噪声,从而保证系统在整个频段范围内都具有极其优秀的噪声性能。

3能量采集

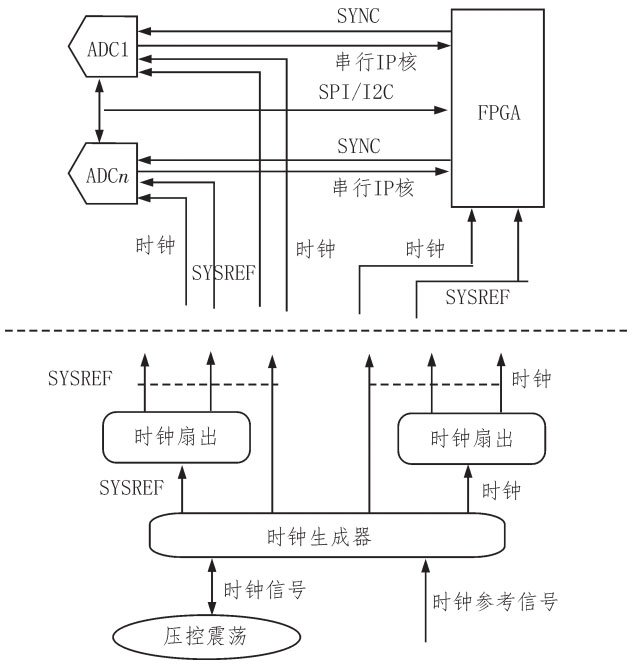

3.1多路ADC同步

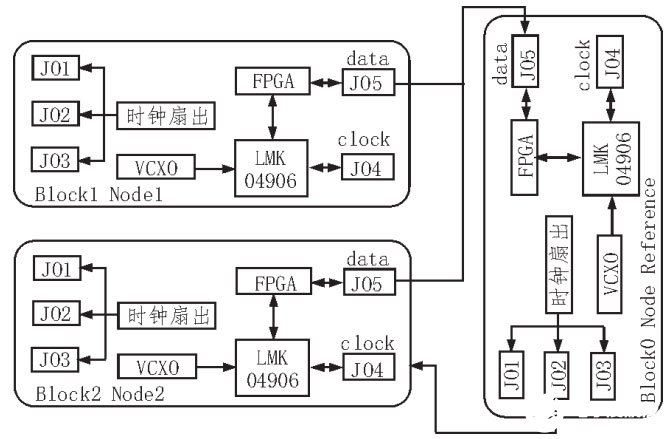

TOF-PET系统是一个多通道并行处理的复杂电子系统,需要对数百个通道同时进行采集与处理,传统PET系统中多路模数转换器(ADC)输出的大量并行信号过多的占用了FPGA处理器的IO资源,随着能量通道数目的增加,所要求的FPGA性能越来越高,最终会导致设计成本高且系统难以实施;除此之外,多通道之间的同步性也会受到PCB布局布线及面积的限制。为了解决多路ADC过多占用FPGAIO资源的问题,设计采用具备JESD204B接口的ADC,将时钟嵌入比特流,利用时钟恢复技术完成多片ADC的同步。

基于JESD204B的串行ADC采集方案如图3所示,ADC上电后,FPGA通过微控制器向控制台计算机获取ADC和时钟生成器的配置信息,并通过SPI或I2C总线对时钟生成器进行配置,判断其工作是否稳定。待其稳定输出后,通过SPI/I2C配置ADC,判断ADC时钟是否锁定,JESD204B接口是否就绪,在以上基础上,开始初始化高速串行转换器的IP核,初始化完成后,置低SYNC信号,系统开始通信。

图3JESD204B串行ADC采集方案

在通信过程中,JESD204B发送器向接收器发送K字符码流,接收器使用时钟数据恢复技术在数据流中对K字符进行检测和定位,然后向时钟生成器输出SYSREF请求信号,以便建立本地多帧时钟。与此同时,SYSREF信号对齐ADC采样时钟,保证所有的采样同时刻进行。在对齐阶段,发送器向接收器发送四帧,接收器对比其中一帧的链路配置参数,匹配成功则进入接收阶段,否则重新置位SYNC信号,重新建立通信。接收器将接收的串行PET能量数据解码、分流转换成并行数据,以供后续处理。

3.2PileUp处理

在高剂量放射源激发条件下,大量高能粒子在短时间内到达探测器,产生信号的堆积,导致信号的脉冲能量被错误的识别,影响空间定位的精度。针对这一问题,本文首先对ADC采样信号进行求导,确定出上升沿的位置,判断两个相邻上升沿之间的时间间隔是否小于设定阈值,若小于阈值,则对其进行PileUp处理,重建流程如图4所示。

图4能量采集链路流程图

在PileUp事件的处理中,无PileUp堆积的单个光子信号按照指数模式进行拟合,如下:

y=Ae-Bx

y为信号采集幅值,x为采样时刻,B为衰减时间常数。如果两个相邻光子被击中的时间间隔小于系统死时间则对前一个事件进行指数拟合,完成其能量的提取。

经过以上处理之后,将采集得到的能量信号通过数字化积分的方式计算出其能量,并利用PET系统重心法得出被伽马光子击中的晶体位置,完成对LOR响应线的空间定位。

4时间提取

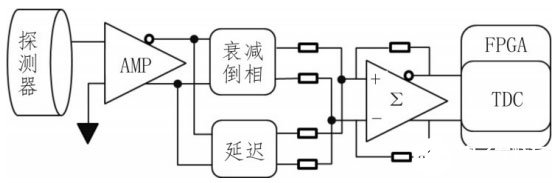

图5CFD定时甄别电路图

由于将探测器的输出信号转换为差分信号,则在后续恒比中不必使用过零比较器,并且信号过零点的时间不因输入信号的不同而受到影响,克服探测器输出信号幅度游动带来的定时误差,实现前端电子电路的定时性能和电路规模的平衡。

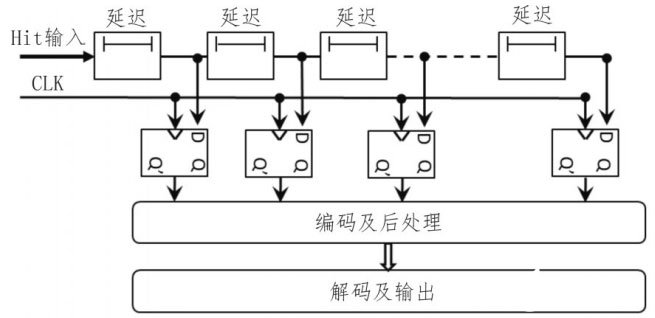

图6FPGATDC工作流程图

相比于专用的ASICTDC芯片,基于FPGA内部专用延迟线结构的TDC技术以其易于集成、可重复利用,低成本、灵活易调试的优点逐步用于基于TOF技术的时间测量系统中,其结构如图6所示。经过CFD定时触发的光子信号到达FPGA管脚后,进入延迟链内,通过时钟完成粗计数时间的测量,通过编码完成细计数时间测测量,最终输出光子的到达时间,以供后续符合处理。

5结果与测试

5.1时钟抖动

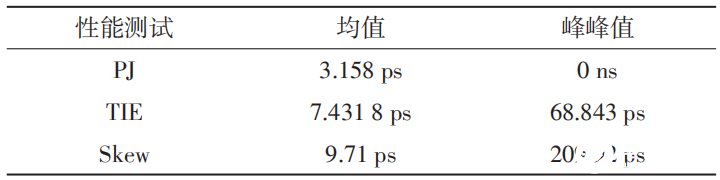

图7全局时钟性能测试

全局时钟性能测试如图7所示,两块电路板使用同一个时钟源扇出,由同轴电缆进行连接,利用示波器对其终端进行测试,时间间隔误差采用示波器的专用测试分析软件,其测试结果如表1所示。其中周期性抖动(PJ)是对时钟周期的变化进行的统计,为短期抖动行为;时间间隔误差(TIE)是信号在电平变换时,其边沿与理想时间位置的偏移,为长期抖动行为;相位输出延时(skew)为两个时钟上升沿的延时值。

测试结果表明基于LMK04906去抖芯片的全局时钟同步设计精度高、可靠性好,可以满足TOF-PET系统的需求。

表1全局时钟性能测试结果

5.2能量链路

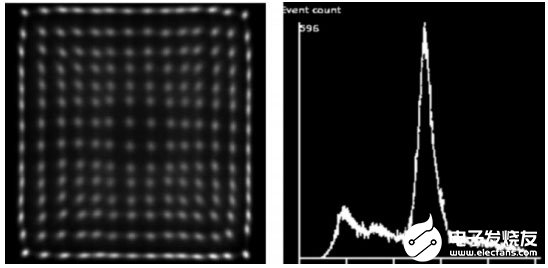

能量链路的测试通过现有系统集成的晶体、光导及PMT探测器前端进行验证,并对基于JESD204B标准的高速ADC采集信号进行处理,得到的晶体位置图及相应的系统能谱图如图8所示,结果表明在能量链路空间定位过程中,晶体位置可以被清晰的分辨,且测得的能量分辨率值低于12%,满足整个系统的设计要求。

图8晶体位置图与系统能谱图

5.3时间链路

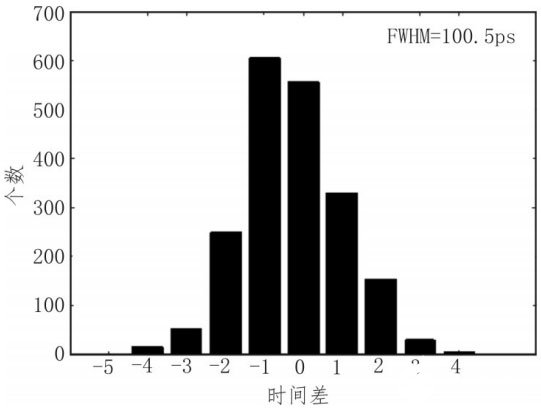

在时间链路的验证上,实验通过信号发生器产生两路具有固定相位差的信号,经过CFD鉴别分别进入FPGA-TDC中,得到FPGA-TDC的码密度图,如图9所示。

图9FPGA-TDC码密度测试

通过建立延迟链与测试时间之间的关系,完成对光子到达时间的测试,得到统计结果的直方图,如图10所示,并用直方图高斯拟合的半高宽来表征伽马光子成像时系统的时间分辨率。从测试结果可以看出前端电子系统拟合的FWHM为100.5ps,满足TOF技术的设计要求。

图10基于FPGA-TDC的TOF分辨测试

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)