本篇要分享的是基于Xilinx FPGA的视频图像采集系统,使用摄像头采集图像数据,并没有用到SDRAM/DDR。这个工程使用的是OV7670 30w像素摄像头,用双口RAM做存储,显示窗口为320x240,而且都知道7670的显示效果也不怎么样,这是一次偶然的机会我得到的资源,便在basys3、zybo、国产FPGAPGT180H上移植成功,总体的显示效果也是可能达到7670应有的标准,7670可以说是最基础的摄像头,基础到你都不想学驱动它,因为画质很差,还有一款基础的摄像头是OV7725,也是30w像素和7670比起来,差别咋就这么大呢(看价格就明白了)。当然这只是一个基础,博主日后也会着手去深入学习基于FPGA的摄像头的驱动。

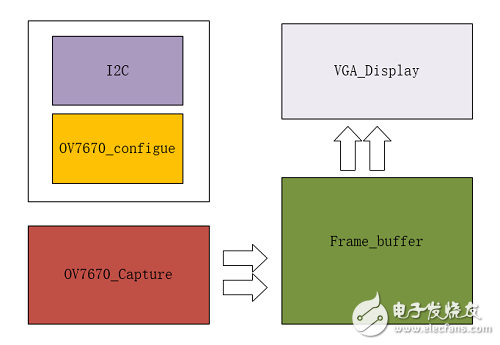

这是本系统简单的结构框图,主要有摄像头配置模块、图像数据采集模块、像素数据存储模块、VGA显示驱动模块组成。

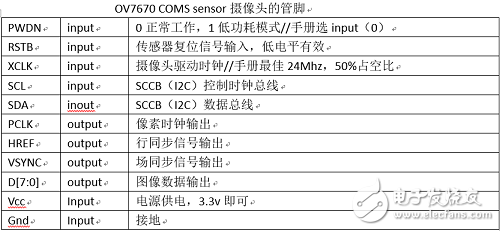

摄像头模块需要用SCCB协议进行配置,SCCB即我们常说的I2C总线。

该部分由两个模块构成,I2C总线模块,摄像头寄存器存储模块,通过I2C总线,也就是下文的SCCB总线,将摄像头寄存器存储模块中的数据发送到OV7670内,完成摄像头的得配置。

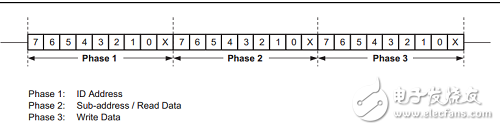

SCCB总线在写寄存器时,先写设备地址(0x42),收到从设备应答后再写寄存器地址,最后写将要写入的寄存器的值。

SCCB总线的读取寄存器时序:SCCB总线在读寄存器时,分两个阶段:第一阶段为先写设备地址(0x42),然后再写寄存器地址;第二阶段为写设备地址(0x43),然后读出寄存器地址的值,从而完成对一个寄存器值的读取,

I2C协议有两条总线,时钟总线sclk和数据总线sdat,我们在时钟总线为高电平的中心时采集数据,在时钟总线为低电平的中心改变数据,每发送8位数据会有一个应答。

I2C协议写 *** 作,先给一个写命令,然后接着两组8位的数据,这个工程里OV7670一共有165个寄存器需要配置,当第165个寄存器配置完成后config_finished信号拉高,表示寄存器配置完成。

从模块引脚上我们可以看到,7670是8位的像素数据输出,场信号(默认低有效),和行信号有效的同时,开始捕获数据,寄存第一个数据,拼接到第二个数据,实现一个完整像素的输出。

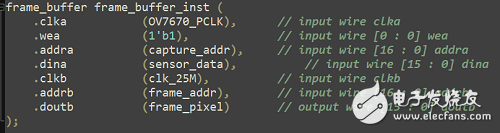

像素数据存储采用的是双口RAM,将RAM数据位宽设置为16,因为我才用的zybo开发板是16位的,深度设置为320x240 = 76800。这是RAMIPCore的顶层实例化。

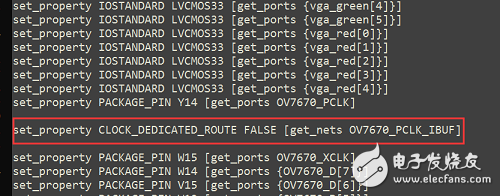

最后是VGA显示模块,将储存的数据读出,显示在VGA显示器上,这样这个视频采集系统就完成了。这里值得一提的是在使用zybo开发板进行摄像头配置的时候出现了如下问题,最后经上网查阅资料最后得以解决,出现这个问题的原因是,遇到上面的问题是因为我们将外部输入的一个时钟管脚 OV7670_PCLK(摄像头输出给FPGA的像素时钟)分配到了一个普通的IO口上面,如果是用一个专用的时钟管脚,比如说ZedBoard有专有时钟管脚 Y9就不会出现这样的错误了。

因为是IO管脚上,所以其周围没有全局时钟 BUFG,所以我们在 XDC 里使用:set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {OV7670_PCLK_IBUF}] 来屏蔽 Xilinx 的检测,从而通过编译。这个方式在软件提示的错误中也提供了解决方法,

我这里使用的迪芝伦官方出品的zybo开发板,肯定有朋友好奇我的摄像头是怎么插上去的——杜邦线啊,引脚约束文件可是我精心设计的,所以只需要18根连排杜邦线即可,使用杜邦线的显示效果基本不会受影响,如果你的显示效果很差,可不能怪杜邦线肯定是你时序的问题。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)