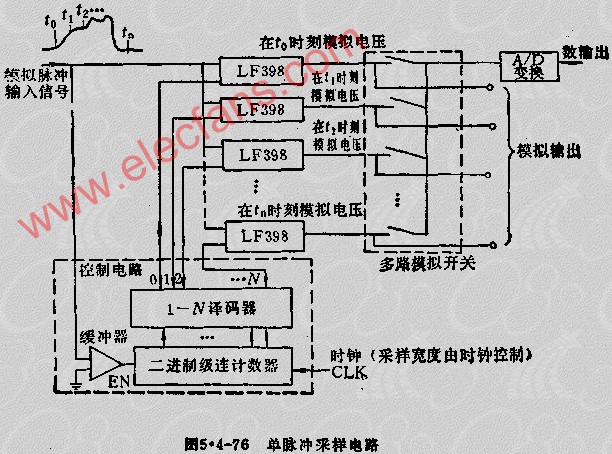

图5.4-76是一单脉冲采样电路。它由N个相同的采样电路,一个模拟多路开关和控制电路组成。当输入的单脉冲电平达到某一阀值时使缓冲器输出启动计数器电路开始计数,计数器的输出送到译码器,其输出就产生相应的输出,作为采样信号,接通相应时刻的采样保持电路。这样在不同的时刻,输入的模拟信号就被在不同时刻的采样电路真实地保存下来。当该模拟信号消失后,可以再接通多路模拟开关重现单次出现的模拟信号。假如控制器是由一个4位二进制计数器和一个四线十六选一译码器组成。在FO时刻,计数器输出为0000,译码器的输出0端产生一个采样脉冲,则FO时刻时,计数器的输出为0001,译码器的1输出端产生采样脉冲,则F1时刻的模拟电压就保持在第二个LF398中......,直到FN时刻为止。

本文地址:https://www.elecfans.com/arTIcle/analog/2010/20100524218430.html

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)