本来不论PT100还是PT1000,他们的采样电路网上都很多,而且之前直接用的是现成的MAX31865方案,奈何领导说太贵,用集成运放搭吧! 领导动动嘴,属下跑断腿!于是各方论坛+度娘!终于整了个有希望的方案,仅以此文记述这段硬件方案设计的经历! 本来想等PCB打板测试后再发出来的,可是后来想想应该先发出来给论坛的大神们看看,到时候哪里要是有问题还可以及时修改,毕竟打板费再少也是肉啊!所以如果方案有问题,拜托各位大佬指正下!

一、目标背景和难点

本次采用的为三线制的PT100,因为嫌弃原有的集成采样驱动芯片贵,这一这次的方案是全部用集成运放来做,然后直接给MCU,哪怕是ADC采样芯片也不允许出现,不过好在精度不高,温度在1度就可以! 在分析下输入输出范围:

(1)MCU的常规采样精度 3300mV/4096=0.8mV;

(2)PT100温度变化一度,阻值变化约0.38Ω;

因此有以下几个难点

(1)阻值变化较小,则对温度或者电压波动比较敏感;

(2)PT100的共性问题,线阻的影响;

(3)阻值变化较小,则前级电压变化较小,容易有杂波信号干扰;

(4)阻值变化较小,即电压变化小,且不可提供较大的电流,否则会给DCDC或LDO造成较大的压力,且后期的低功耗也没法处理,这样的话MCU采样难度增大;

二、大概方案

针对以上难点,在网上也查了不少方案;主流的就是恒流源+滤波电路,所以决定也采用这种电路;原因很简单:1、大家都说好,才是真的好;2、毕竟资料丰富容易找,后面出了问题,也知道从哪里查起!虽然主流框架确定了,但是很多细节还是值得琢磨的,这个后面说,先说方案!

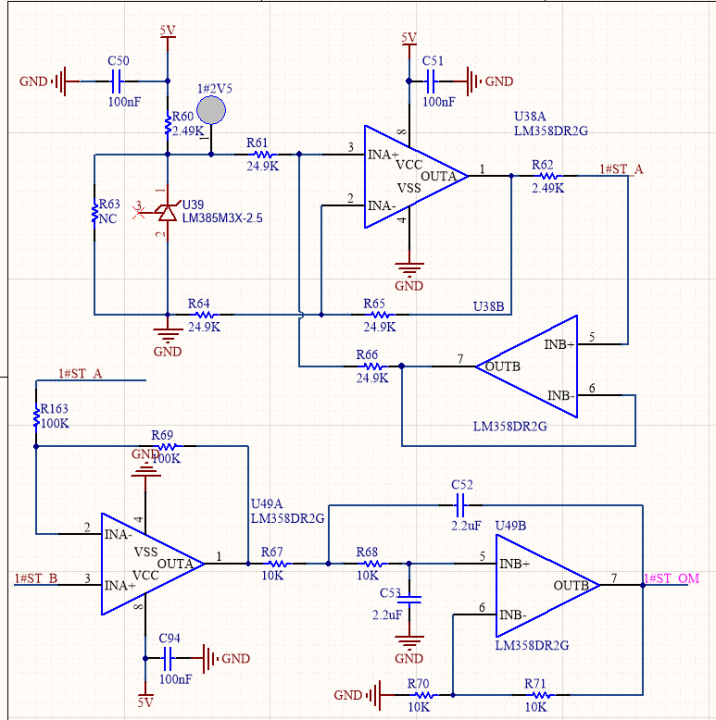

如上图:

(1)U38A和U38B构成的是1mA的恒流源电路,使PT100的变化更加的线性化!其输入端采用电压基准产生2.5V的电压,输出电流的大小取决于R62,即I=2.5/R62; (2)U49A作为PT100采样信号的输入级!PS:这个电路是网上查到的,说是能消除PT100的线阻影响,具体原理还没整明白,只是先拿来用; (3)U49B是一个二阶的滤波电路,截止频率在20Hz以下; (4)U58A就是一个同相的比例运放,作为输出放大,将滤波后的信号放大11倍给MCU;

三、细节处理,尽量避坑

关于运放,一般简单应用场景下,一旦运放型号选定了,需要注意的其实就是那么几点。其中主要的大概就是阻容的配比了,这个计算太复杂了。PS:除了知道虚短虚断其他的都不清楚

不过好在有mulTIsim,一个大概的方案框架确定了,接下来就是将电路搬到mulTIsim中仿真就是了!包括上图中元器件的参数都是仿真之后调整过的,而且最 开始连输出的那个比例运放都没有,但是仿真过程中发现有问题!前两天针对这个问题还发过帖子,还好有大神 KING5555的指导!废话少说,上图:

如图对整个采样电路进行仿真,其中探针1的参数可以看到,直流电流是恒定的1mA,虽然有些交流的信号成分在里面,但是幅值太低对输出没啥太大的影响。 R7模拟PT100,R13,R14,R15模拟线阻,虽然有点大了! U1A组成二阶低通滤波电路,本来开始想着直接修改滤波电路的增益,即R10和R11的比值的,但是修改后发现探针1上的交流信号幅值很大,严重影响了后面的输出,除非修改输入滤波电容的值,但是修改后的截止频率太高,达不到滤波效果! 如下图:

后来在论坛发帖经KING大神的解释,然后去网上搜了下,才知道由于这种正相的滤波器,增益本来就没法设置过高,不然就会因为自激振荡由滤波器变为振荡器了!所以随后就开始考虑使用反向输入的低通滤波框架!

本来确实是有效的,实现了增益和滤波并存,但是他也有自己的特点,比如说:因为是反相输入,那么输出应该是负的,如果是轨到轨的运放,那么我需要一个负电源,且给MCU之前还需要反相一下!光这一点就给他PASS掉了! 所以最终决定还是用正相输入的滤波电路然后后面加个普通运放做放大处理!剩下的就是看是否满足使用场景需求了!

如图,这三个图分别为PT100,在100Ω,100.38Ω,138Ω三种阻值下对应的输出电压,可以看出变化一度即0.38Ω时,ΔU=2.1933-2.1849=0.0084V,即8.4mV,换算成ADC的采样精度,大概在10个单位,针对温度一度的精度要求,给MCU所留余量基本足够!而且温度100度时,对应的电压为 3.0196V,也没有超出运放的输出和MCU的输入阈值!!! 最后在看滤波电路的滤波效果!如下图,截止频率在10Hz左右,也满足了目标要求!!!

PS:正在画板中,有不足的地方,各位大佬快来拍砖,多多益善,可以都预留上,总比后面实物做出来飞线来的清爽!!!

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)