引言

抖动(jitter)会使数字电路的传输性能恶化,由于信号上升沿或是下降沿在时间轴上的正确位置被取代,在数据再生的时候,数据比特流中就会引入错误。在合并了缓冲存储器和相位比较器的数字仪表中,由于数据溢出或是损耗,错误就会引入到数字信号中。此外,在数模变换电路中,时钟信号的相位调制会使恢复出的采样信号恶化,这在传输编码的宽带信号时会造成问题。

1 抖动的分类

抖动分为系统抖动和随机抖动。

(1)系统抖动是在信号再生电路时间上不准,或是码是串扰,或是在幅频转换中的不准确的电缆均衡造成的。系统抖动取决于系统的性能。

(2)随机抖动来源于内部或是外部的干扰信号,如噪声、串扰、反射等。随机抖动与传输信号的系统无关。

系统抖动与不同的脉冲再生电路的脉冲的模式有关,会连续地积累。随机抖动则与脉冲再生电路的脉冲模式无关,而且也不会连续地积累;在大多数低速率的数字系统中,系统抖动占主导地位;而在高速系统中,随机抖动变得越来越重要,甚至会占据主导地位。

干扰性的抖动可以利用信号再生电路划中利用“去抖动”电路来减弱其影响。这种“去抖动”电路来减弱其影响。这种“去抖动”电路包括了一个带有窄带相位平滑电路的信号缓冲器。信号再生电路只能将抖动频率高于时钟再生电路的截止频率的抖动成分减小,而低频的抖动成分则仍然会出现在输出信号或是信号再生电路中。在这种情况下,抖动被传输到输出信号中,信号再生电路此时就象是一个低通滤波器。

2 抖动测量方法

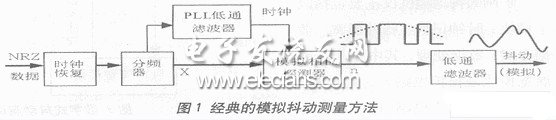

传统的抖动测量采用模拟测试的方法。图1给出了传统模拟测量方法的原理框图,它是将数据信号与基准时钟信号相比较,使用相位探测器的平均输出。模拟测量方法带来了很多问题,这都是因为相位探测器将相位表达成一个模拟电压引起的。

2.1 用模拟方法测试抖动的缺点

a 时钟恢复限制了抖动测量的带宽;

b 时间恢复由于自由运行频率的偏移引入了抖动噪声;

c 大动态范围要求大频率分割,导致产生了起出相位探测器范围的低频脉冲,进一步限制了测量的带宽;

d 模拟电压受制于由噪声和寄生电容产生的负面影响;

e 模拟电压的范围受制于电源电压的范围;

f 基准恢复由于其带宽小获得锁相很慢。

随着DSP技术、ADC应用技术和ASIC技术的发展,抖动分析跟随着科技从模拟到数字的转变进程,发展了基于数字分析的抖动测量方法。基于数字的抖动分析方法有先进得多的特性,能使工程师们为下一代设计的测试和分析作更充分的准备。

下面图2给出了基于数字分析的抖动测量方法的原理框图。这里的目标是将每个NRZ沿用二进制数作时间标记,其中计数器最低位(LSB)权值就是时间间隔分辨率。时间间隔计数器完成时间标记功能,通过数字处理标记出抖动大小,再经过数字滤波器提供抖动测量所需的高通和低通滤波。在滤波过程中,可实现分辨率中两个最佳位。抖动得到进一步的处理以检测峰峰值、真有效值或其它参数,比如频谱容量。

2.2 数字化的抖动测量的优点

a 具有更宽的带宽和更低的噪声,因为它不需要时钟恢复。

b 具有更宽的带宽和更光滑的频率响应,因为数字相位探测器将每个NRZ沿以时间标记(不需要对模拟脉冲作平均处理)。

c 具有更低的抖动噪声,因为数字时间标记不受噪声的影响。

d 增益误差率只有0.01%,因为信号处理是完全数字化的。

e 动态范围超过4000UIp-p,同时保持0.01UI的分辨率。

f 测量时没有延时,因为不使用锁相环信号去获取时钟。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)