那么,什么是EMC设计?

首先,EMC设计审核并不是一个完整的评论,相反,它侧重于特定的EMC问题,它没有解决其他问题,如可靠性,热量,功率,重量等,最好留给更正式的评论。

根据产品的不同,EMC设计审查可以解决电路板问题,机械问题或系统级问题。同时,它还涉及需求(法规和/或威胁),约束(成本,数量等)和设计策略。

什么是EMC设计审核的最佳时间?

对于大多数项目,EMC设计审查的理想时间是在最初的电气和机械设计阶段,对于电路板,很好的时间是电路板布局完成,第一件艺术品准备就绪,在这个阶段,设计通常足够坚实,可以提出建议,但流动性足以做出改变。

大多数EMC审核可在一天或更短时间内完成,对于简单的系统或单个电路板,即使几个小时也可能就足够了,但是不要自己做这一切,多和同事一起讨论这些问题,通常向其他人解释设计的方法能跟快解决问题。

在进入设计评估之前,必须完成四项初步任务,如下所示:

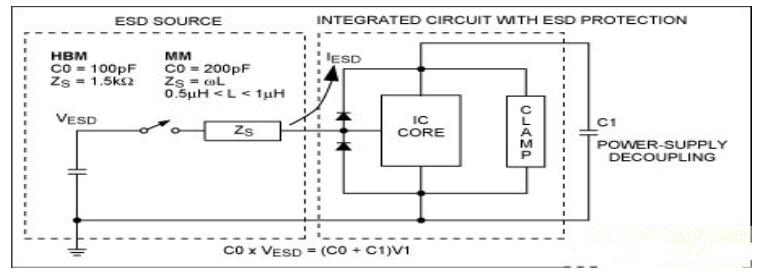

1.识别和评估EMC威胁-典型威胁包括来自附近发射器的射频(RF)能量,来自人或其他来源的静电放电(ESD),电源干扰以及传导/辐射发射(可能对其他电子设备产生不利影响)。

这些通常被指定为测试要求,但您可能需要根据实际预期环境对其进行修改,例如,在对医疗器械的一次审查中,我们询问它是否将用于陆地和空中救护车。如果答案是肯定的,原来的办公室/家庭要求被认为是不合适的。

顺便提一下,该制造商最终开发了两个产品系列,救护车产品的硬化程度高于家庭/办公室产品,并以高价出售。什么可能导致一些棘手的EMC问题产生额外的利润,同时抢先解决意外的客户问题(良好工程的一个例子!)。

2.确定影响或受这些威胁影响的关键电路或组件-数字电路(特别是复位和控制电路)非常容易受到尖峰和瞬变的影响,而模拟电路非常容易受到RF影响。数字时钟(和其他高度重复的信号源)是丰富的辐射发射源。电源电路易受电源干扰,也可能导致传导发射。

3.确定可能影响EMC设计决策的其他设计约束-包括成本,数量,重量,空间和不合规成本(CONC),顺便提一下,在成本非常敏感的情况下,我们经常提倡设计就地固定器(例如电容器的焊盘),以后可以根据需要使用EMC组件进行填充。不要忽视后者-作为工程师,我们总是需要一个后备计划。

4.确定适当的EMC设计功能-这就是设计乐趣的开始。电路板是一个理想的起点。毕竟,所有电磁干扰EMC问题最终都会在电路中开始和结束。当然,如果您不设计电路板,您将在系统级别工作。这可能包括机械问题(屏蔽)以及电缆,连接器,电源和接地。许多(但不是全部)防御项目属于后一类。

以下是检查电路板的十个关键点:

1.时钟电路-这些是高频辐射发射的主要来源,另外,检查任何高度重复的类似时钟的电路。一些存储器控制和总线控制信号属于这一类。

设计建议包括:

a、Vcc的高频去耦(串联铁氧体提供更多保护)

b、时钟输出串联电阻(典型值10-33欧姆)

c、位于振荡器附近的晶体或谐振器

2.复位/中断/控制电路-瑞典非常容易受到ESD,EFT和瞬态的影响,中断和控制(读/写)也很容易受到攻击。机械开关的外部复位线非常脆弱。

设计建议包括:

a、复位Vcc,参考和输出的高频去耦,走线长度超过两英寸走线长度,考虑使用串联铁氧体进行额外保护。

b、易受攻击的中断/控制电路所需的类似修复

3.模拟电路-非常容易受到RF能量的影响。此外,寄生振荡可能导致不必要的辐射发射。

设计建议包括:

a、Vcc的高频去耦

b、电路输入和输出的高频滤波(典型值为1000pF)

c、所有模拟传感器都有类似保护

4.电压调节器-像模拟电路一样,它们也容易受到RF的影响,由于元件带宽增加,寄生振荡现在在VHF/UHF频率范围内很常见。

设计建议包括:

a、Vcc的高频去耦

b、输入和输出引脚直接高频去耦至芯片中性引脚(典型值为1000pF)。强烈建议防止那些讨厌的寄生振荡。

5.射频发射器和接收器-这些电路带来了一系列全新的潜在EMC问题,板载接收器可能被数字谐波干扰或消失(GPS接收器极易受到攻击),板载发射器可能会堵塞附近的模拟电路。多个无线电可能导致互调和交叉调制问题。

设计建议包括:

a、保护接收器输入(可能需要特殊设计)。

b、RF模块的内部屏蔽

c、时钟管理(避免接收器输入上的谐波)。

d、检查天线位置和电缆布线。

e、DSP或其他软件技术也可能是必要的。

6.电路板叠加-良好的电路板结构对于良好的EMI控制至关重要,幸运的是,大多数修复都是免费的。

设计建议包括:

a、将每个信号层保持在相邻平面旁边。

b、保持相应的电源/接地层相邻。

c、保持对称叠加。

d、考虑外埋地层。

7.分裂平面-交叉切口和不匹配的平面可以严重抵消板上最好的EMI控制,修复这些问题后,我们已经看到了10倍的改进(20分贝),因此,首先要防止它们符合您的最佳利益。

设计建议包括:

a、检查高速走线,并在相邻平面的切口上进行“上下”布线。

b、请注意,如果高频能量潜入这些迹线,切割过程中的低速迹线也会导致问题。

c、始终将电源/接地层对齐为镜像。

8.平面规划和布线-组件的随机放置和随机跟踪路由可能导致EMC问题,有机会,自动路由器经常路由以最大化EMI(Murphy定律的变化)。

设计建议包括:

a、根据频率分离组件,将数字,音频,电源和RF电路组合在一起,而不是将它们全部集中在一起。也分开了痕迹。

b、注意关键迹线(时钟,复位,控制线)的布线。

c、避免将关键电路放置在I/O端口附近。

d、考虑手动布线关键走线以实现更好的EMC控制。

9.保护外围设备-由于电源和I/O连接到外部世界,因此需要特别注意。这从板级开始,也可以在系统级应用。

设计建议包括:

a、根据需要过滤和瞬态保护。至少,在所有电源输入端放置0.01uF电容。

b、注意外部I/O线路上的ESD保护。

10.接地-需要在电路板和系统级别解决的另一个问题,这可能是另一篇文章的主题,甚至是一本书。但是在董事会层面上有很多事情需要检查。

设计建议包括:

a、考虑数字,模拟和电源的单独接地路径。

b、多点接地连接是高速数字(和RF)电路的首选。

c、对于低电平/低频模拟电路,单点接地连接是首选。

d、混合接地(电容器和电感器)可用于混合技术。

e、请注意,额外的接地限制可能适用于恶劣环境,切勿违反安全接地以解决EMC问题。

系统级评审

在这个层面上,我们经常从外到内工作,专注于机械结构,接口(电源和信号)和系统接地,其中大部分假设屏蔽外壳,对于非屏蔽设备,必须在板级实现EMC设计目标。

1.机械-在这个级别,我们对EMC屏蔽性能感兴趣,因此,我们看看材料,机械接头(接缝/覆盖/通风)和不连续性(穿透和开口)。

设计建议包括:

a、检查材料,薄导电涂层(包括箔,涂料和电镀)对高频有效,但通常不适合工频磁场。在后者中,可能需要可渗透材料(钢或mu-金属)。

b、检查不连续性。超过两英寸的任何接缝对于高于300MHz的ESD或RF是有问题的。在1GHz,即使是1/2英寸也可能相当漏水。您可能需要用导电垫圈填充接缝。有关电缆穿透的信息,请参阅下一段。

2.接口-在这个级别,我们检查信号和功率及其连接。这包括内部电缆布局和布线。

设计建议包括:

a、对于信号接口,请使用隔板连接器作为屏蔽电缆。过滤后的连接器甚至更好。没有洞。将电缆穿过外壳中的孔可以完全破坏高频下的EMC屏蔽。我们已经看到它发生了太多次。

b、对于电源接口,隔板过滤器在穿透点处是优选的。如果使用内部模块化过滤器,则必须尽可能靠近穿透点放置。

c、外部电缆-如果可能,检查配套电缆。连接器是关注的关键领域。电缆与连接器的完全圆周结合是优选的。如果它泄漏出外部电缆或连接器,那么您在盒子级别的所有努力都是徒劳的。

3.系统接地-大多数EMC接地问题都在电路级的包装盒内解决,这里主要关注的是不违反系统接地方法,特别是安全接地。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)