通用串行总线(USB)规格的最新迭代版本USB 3.1第2代有望改变IT、消费、工业及通用嵌入式电子设备交换数据和供电的方式。再加之Type-C连接器,它就能够替代许多其它形式的有线连接,而且它已经在便携式消费设备领域呈现迅速增长之趋。

这可能与该规格的供电(PD)方面最为相关。随着Type-C连接器用于更多设备,用户对供电潜能的意识也将会增加。

短期内,预计USB-PD将在离线电源适配器中得以实施,且最有可能用于高端笔记本电脑,这也符合提供更高电源转换能效的趋势。预计至2020年,约半数笔记本电脑适配器都将采用USB-PD。制造商还希望能够优化电器的电源适配器,这可能意味着输出功率在27至100W之间,这也会影响设计。因此如果制造商要生产各种不同输出功率水平的适配器,能够提供设计灵活性的单一方案将成为首选。

电源转换的挑战从交流(AC)转到直流(DC)涉及到转换,且不可避免地会造成相关损耗,半导体行业一直在努力减少这样的损耗。当前存在许多电源转换拓扑结构,一般而言,当将成本视为主要问题且能效并不太重要时,可采用初级端稳压(PSR)反激拓扑结构,特别是当输出功率要求相对较低且无需严格的输出电压稳压时。当需要更高输出功率时,为获得更高的能效和更佳的性能,通常首选次级端稳压(SSR)准谐振(QR)反激拓扑结构。

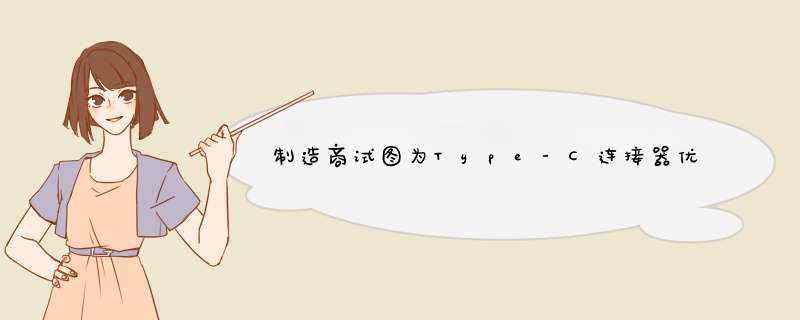

在主电源变压器之后进行的此形式的输出整流,一直用二极管作为开关(图1),然而这也有能效问题,主要是由于在二极管的PN结上经历了正向压降。这通常约为0.7 V,尽管通常采用肖特基二极管可将压降降至更接近0.3 V,但这仍是损耗。

图1:次级端采用二极管整流的经典反激式固定输出电压电源转换方案

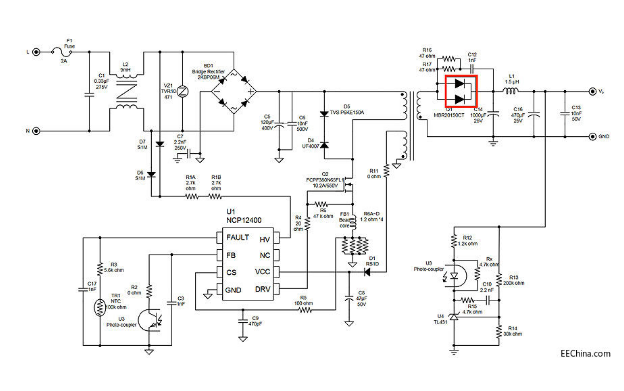

现代高功率密度USB-PD适配器如今通过采用低导通电阻MOSFET来避免二极管相关损耗(图2)。

图2:基于使用MOSFET作为输出开关的次级端同步整流的USB-PD电源适配器

虽然这提供了能效增益,但复杂性也随之而来。使用晶体管而非二极管的做法称为次级端同步整流,为了从这种拓扑结构中获益,设计人员需要添加一个控制器,在正确的时间导通和关断晶体管。更为复杂的是,各种SR控制器都可用,可基于应用程序提供不同的特性与优势。

用于USB-PD的SR控制器相较于采用肖特基二极管,使用一个低RDS(on)(约5至10mΩ)MOSFET也能显着提高次级端输出整流的能效,从而有望实现高于93%的峰值能效。

MOSFET的开关时序现已成为关键参数,导通和关断延迟会直接影响整体能效。由于控制器决定了MOSFET的状态,因此在选择合适的控制器时,由控制器引起的切换延迟时间就成为了需要考量的关键参数。

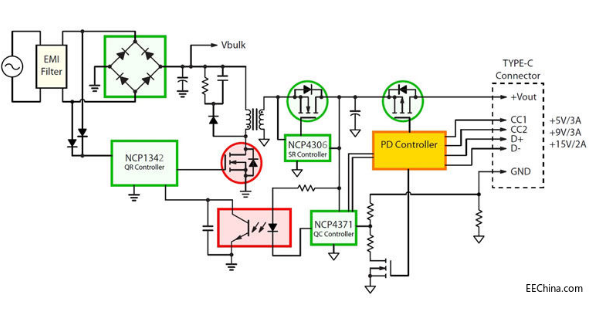

在USB-PD应用中,反激式电源通常设计为以连续导通模式(CCM)或准谐振(QR)模式工作。在CCM中,SR控制器需要非常快速地关断MOSFET,以避免在初级端造成任何击穿,有效地在初级端和次级端之间建立直接通路,这会导致功率MOSFET可能出现非常高的瞬时电流。图3显示了典型的电路配置,其中M1位于初级端,M2(同步整流MOSFET)位于次级端。

图3:开关模式电源示例,显示了初级和次级端晶体管

在此配置中,必须在M1导通之前快速关断M2。为满足100W的USB-PD规格,所选的同步整流MOSFET需要具有足够低的导通状态电阻,以应对所需输出电压需要的电流水平,还要做到最低程度的热损耗,以避免内部适配器温度升至过高水平,这反过来又受到控制器降低电流以确保MOSFET能够在最短时间内关断能力的影响。

要确定何时关断MOSFET,涉及到测量器件漏极至源极端的电压。如果控制器实施直接感测(Direct Sensing),则可以通过很少的附加元件来实现;如果控制器没有实施直接感测,则需要额外的外部元件,这不仅增加了总成本,而且本身会引发额外的延迟,从而降低整体能效。直接感测可避免这种潜在的低能效,且在导通和关断期间都可用。典型情况下,控制器的直接感测引脚需要承受120 V或更高的电压以用于USB-PD应用,为瞬态和异常情况下的瞬时电压尖峰提供足够的余量。

应对功率需求的增加,涉及到导通MOSFET,因此在这种情况下,导通时间延迟至关重要;如果速度太慢,所需电流将流过MOSFET的体二极管而非其沟道,导致无谓的功率损耗和能效下降。

USB-PD适配器的另一个重要考量是符合轻负载和待机功耗限制,如CoC TIer 2和DoE 6级。多数地区都已采用这些或同等标准。无负载时,电源需要能够检测到这一点,同时仍能向控制电路(例如USB协议芯片)供电,但仍然保持低于0.075瓦的输入功率。可检测到此情况并进入轻负载模式的SR控制器能够帮助制造商满足这些要求。

集成、稳健的方案选择满足所有这些要求的次级端同步整流器控制器需要仔细考量可用的方案。如前所述,根据应用,适配器设计将针对特定的输出功率进行优化。可提供这种灵活水平的控制器能够用于多种适配器,通过能提供可调节开关时间的控制器就能实现,时间可在设计时设定。

安森美半导体的NCP4306旨在为上述所有领域提供同类领先的性能。它提供30 ns的导通时间和仅13 ns的关断时间,最大化了同步整流器MOSFET的导通时间,同时消除了与初级端开关交叉导通的风险。它在设计上还能够承受高达200V的直接感测电压。在7A的汇电流下,控制器可轻松驱动小于10mΩ的导通电阻MOSFET,并满足相应的设计要求,使USB-PD电源适配器能够在高达100W的条件下工作。

NCP4306在设计上除了用于驱动经过试验和测试的中压MOSFET之外,还有一种可用于驱动氮化镓(GaN)高电子迁移率晶体管(HEMT),能够比MOSFET更快地开关。该同步整流器控制器可为GaN提供稳定的驱动电压(典型值为5 V),而不会对其门极造成过压,否则可能会导致器件发生故障。这使其适用于在QR模式下,甚至有源钳位反激式拓扑结构中工作的超高密度电源适配器。该同步整流控制器的最大工作频率高达1 MHz。图3显示了典型应用中的NCP4306。与可实现高达500 kHz的高频QR主控制器NCP1342一同使用时,可实现峰值能效达到93.5%且功率密度接近20W/in3的USB-PD适配器设计。

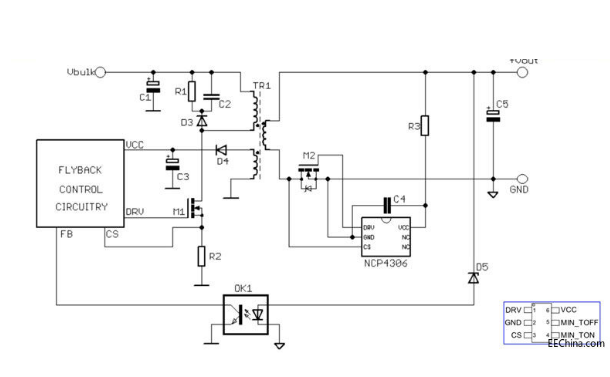

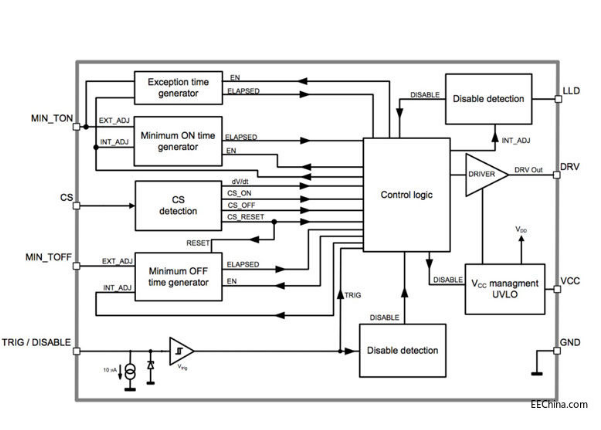

该器件内部包含用于设置最小导通时间和最小关断时间消隐周期的模块(见图4),以对抗由PCB布局和其他寄生元件引起的振铃,如上所述,这可能导致无谓的体二极管导通。两个时序参数都可通过外部电阻进行调整,从而为所需的功率输出和选定的功率元件优化设计。轻负载检测(LLD)模块可检测输出负载降低时电源在跳周期模式下工作时的开关脉冲频率降低,并将同步整流器控制器放入禁用模式。该控制器在该状态下消耗的电流非常低(通常为37 mA),从而使USB-PD电源适配器能够符合或绰绰有余地超过CoC TIer 2要求。

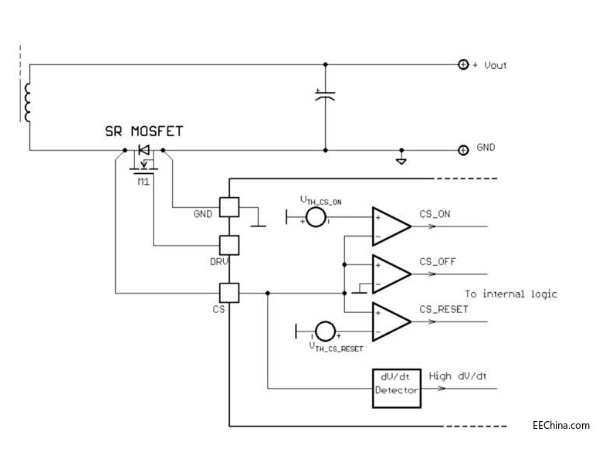

图5显示了控制直接感测功能的内部电路。一旦连接到开关漏极端CS引脚上的电压低于VTH_CS_ON阈值,同步整流器MOSFET M1就会导通。一旦CS引脚上的电压高于VTH_CS_OFF(通常为0.5 mV),MOSFET就会关断。 NCP4306的直接感测模块内还配备了dV / dt斜率检测器,以区分闲置状态下的谐振振铃和实际主开关导通的情况。这对于具有不同输出电压和负载曲线的USB-PD设计尤为重要,且有助于确保控制器在需要之时可激活MOSFET。

图4:NCP4306内部模块框图

图5:NCP4306实施直接感测,可承受高达200 V的电压

结论在可预见的未来,使用Type-C连接器通过USB供电预计将主导电源适配器的设计,其在许多应用领域的采用已经非常突出,它的多功能性意味着它将成为制造商和消费者的首选方案。

选择正确的SR控制器对于设计一个优化的适配器至关重要,这样的适配器不仅符合能效法规,还能满足消费者的严苛要求。NCP4306代表了新一代SR控制器中首款能够提供这个级别的性能和灵活性的产品。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)