摘要:本文简要的总结了在高速数字设计中串联终端匹配和并联终端匹配的优缺点,并对这两种匹配方式的终端匹配电阻处于不同位置时的匹配效果做了相应的仿真和深入的分析,得出了串联终端匹配电阻对位置的要求没有终端匹配电阻严格这一结论,给出了一些关于终端匹配电阻摆放位置的建议。为在PCB 设计中如何放置终端匹配电阻提供了理论和实践上的指导。

1 引言

随着半导体工艺的快速发展,信号上升时间愈来愈短,导致信号完整性问题日益突出;另外,器件小型化趋势也日益明显,电路板的面积也越来越小,因此对PCB 板的布局要求也日益严格。这就要求高速PCB 设计工程师严格的去考虑各种器件的放置问题,包括滤波电容、匹配电阻等,在提高系统的信号完整性的同时节省印制板面积。本文利用Mentor 公司的Hyperlynx 仿真软件对简单并联终端匹配和串联终端匹配方式进行了仿真和分析,研究不同位置的匹配电阻对信号质量的影响。

2 并联终端匹配和串联终端匹配的优缺点

在高速数字设计中,电阻常被用来对传输线进行阻抗匹配,以消除传输线上的反射。最典型简单的匹配方式有两种:简单并联终端匹配和串联终端匹配。简单并联终端匹配电阻与具有极高输入阻抗的接收端并联,并且接地或者电源,以消除接收端的反射,优缺点是能够比较精确的选择匹配电阻的阻值但是将消耗直流功率功耗。串联源端匹配电阻与小输出阻抗的驱动器串联,以吸收接收端反射回来的信号,此方式的优缺点是不消耗功率但是由于许多驱动器都是非线性的,如TTL 器件,其输出阻抗随着器件逻辑状态的变化而变化,从而导致匹配电阻的阻值难以确定。故在要求低功耗的数字设计中,串联终端匹配方式更常用;并联终端匹配方式更多的使用在模拟电路设计中,以牺牲功耗来满足其高精度的要求。本文将总结出串联终端匹配方式的另一优点即其匹配电阻在PCB 板中对位置的要求没有简单并联终端匹配方式严格。

3 匹配电阻位置的变化对信号波形的影响

3.1 并联终端匹配情况-匹配电阻位于接收端之前

如图1a 所示,我们构建了三组终端匹配的结构。第一组结构中终端匹配电阻直接与接收器相连(理想状态,图1a 上);第二组结构中终端匹配电阻位于距离终端0.5in.处(图1a 中),即有0.5in.的传输线没有被匹配;第三组结构中终端匹配电阻位于终端1in.处(图1a 下)。驱动器和接收器模型选用Hyperlynx7.0 自带的简易IBIS 模型:CMOS,3.3V,FAST(该模型驱动波形的上升时间约为1.5ns)。传输线特征阻抗为92.9 欧姆,传输线总长为20in.(约为0.5m 左右),总的延迟时间为2.975ns,线宽为6mil。驱动信号的频率为100MHZ,

300)this.width=300" border=0>

300)this.width=300" border=0>

300)this.width=300" border=0>

300)this.width=300" border=0>

图1b 为使用Hyperlynx7.0 仿真工具得到的仿真波形,如图所示,有明显延迟的三组波形为接收端波形,其中幅值最低的为匹配电阻位于理想状态时的波形;幅值最高的为匹配电阻位于接收端前1in.处的波形;中间的为匹配电阻位于接收端前0.5in.处的波形。测得三种情况下接收端电平最大幅值分别为3.4V,3.7V,4.1V。从图 1b 和表1 中可以看出终端匹配电阻与接收端之间的距离每增加100mil,信号过冲就将增加几十毫伏,可见,改变终端匹配电阻的位置的确会给信号质量带来很大的影响,原因是如果匹配电阻距离接收器很远,将有一段可被视为传输线的PCB 连线得不到应有的阻抗匹配,从而导致信号在接收端产生反射现象,反射到驱动端的信号将再次反射回接收端,这样就会大大降低了接收端信号的质量。因此在高速 PCB 设计中应设法使得这样一个分支长不超过100mil。

表1 并联终端匹配电阻位于接收端不同位置时测得的接收端信号最高电压值

300)this.width=300" border=0>

300)this.width=300" border=0>

3.2 并联终端匹配情况-匹配电阻位于接收端之后

当然在具体的PCB 设计中,由于种种原因设计者也许无法将终端匹配电阻放置在接收端之前,那么只能将其放置在接收端之后。在图2a 中,上半部分为终端匹配电阻位于理想位置的情形(即直接与接收器相连),下半部分为终端匹配电阻位于接收器之后的情形,匹配电阻与接收器之间有一段 1in.长的传输线。图2b 为图2a 对应的仿真波形,可见,在匹配电阻位于接收器之后时,接收端的波形非常接近匹配电阻位于理想位置的波形,只是波形的延迟更大,经测量得到这个延迟近似等于这个电阻与接收器之间的传输线的延迟。

因此可以得出结论,将终端匹配电阻放置在传输线之后几乎不会影响其匹配效果。在实际的PCB 设计中,完全可以采取这种做法以尽可能的使匹配电阻的位置接近理想的状态,这是一种很好的选择。

300)this.width=300" border=0>

300)this.width=300" border=0>

300)this.width=300" border=0>

300)this.width=300" border=0>

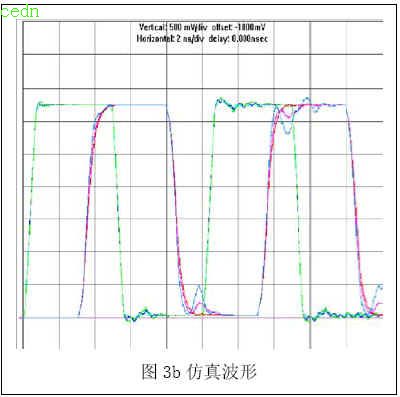

3.3 串联终端匹配情况

图3a 构建了三种源端匹配结构,类似于终端匹配的情形,这三种结构分别为匹配电阻直接与接收器相连(理想情况);与接收器相距0.5in.;与接收器相距 1in.。图3b 为图3a相对应的仿真波形。从波形中可以看出,三种情况下的仿真波形变化不是太大,远没有终端匹配那样剧烈。测得三种情况下接收端电平最大幅值分别为: 3.256V,3.266V,3.366V。

从下表2 也可以非常明显的看出源端匹配电阻的位置变化并不会给信号质量带来很大的影响。

300)this.width=300" border=0>

300)this.width=300" border=0>

300)this.width=300" border=0>

300)this.width=300" border=0>

表2 串联终端匹配电阻位于驱动端不同位置时测得的接收端信号最高电压值

300)this.width=300" border=0>

300)this.width=300" border=0>

从前面的分析可知,串联终端匹配电阻主要用于吸收从接收端反射回来的信号,由于接收端输入阻抗很大,可以视为开路,所以信号到达接收端时将产生全反射,反射回的信号能量大部分将被驱动端的匹配电阻和驱动器吸收,因而从驱动端二次反射回来的能量很少,故串联终端匹配电阻适当的远离接收端放置,不会严重的影响接收端的信号质量。但对于并联终端匹配来说,如果匹配电阻远离接收端放置,接收端之前将有一段传输线得不到匹配,而且驱动端没有串联终端电阻不会吸收掉从接收端全反射回来的能量,因而信号将来回反射,使得接收端信号的质量大大降低。这是串联终端匹配电阻对位置的要求没有并联终端匹配要求严格的部分原因。

4 结论

通过上文对并联终端匹配电阻和串联终端匹配电阻处于不同位置情形的仿真和分析研究,可以得出结论即串联终端匹配电阻对位置的要求没有并联终端匹配电阻严格,也就是在实际的PCB 设计中,可以适当的将串联终端匹配电阻远离驱动器放置而不必担心这样做会给系统的信号完整性带来很大的问题。另外,仿真结果显示使用并联终端匹配方式时将匹配电阻放置在驱动器之后也不会对信号波形产生很大的影响。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)