1 基于CPLD的片内环形振荡器

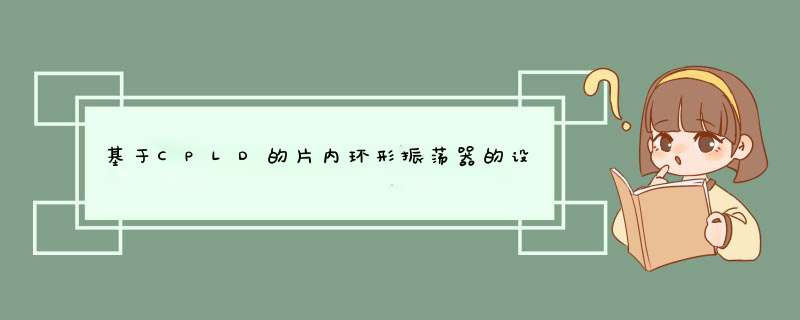

环形振荡器原理如图1所示。由奇数个非门组成的环形非门级联串使电路处于无稳定状态,静态下任何一个非门的输入和输出都不可能稳定在高电平或低电平,而只能处于周而复始的高低电平转换状态,从而产生自激振荡。振荡周期为T=2Ntpd,其中N是非门的个数,tpd是每个非门的传输延迟时间,改变电路中非门的数量可以改变电路的振荡频率。

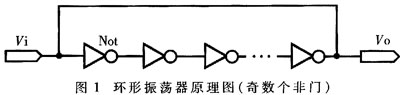

图1所示的环形振荡器即使采用电路原理图输入,经电子设计自动化(EDA)软件综合后,也得不到对应的电路结构。实际上,EDA综合工具不是从电路结构出发,而是从电路输入和输出的逻辑关系出发给出综合结果,所以,奇数个非门的级联将被综合为一个非门,而偶数个非门的级联被综合为一个缓冲或一条联线。为能在CPLD器件中实现图1的环形振荡器结构,本文将图1中单端口输入元件改成二端口输入元件,即用二输入与非门代替图1的第一个非门,其余偶数个非门则用二输入与门代替,二端口元件的一个输入端口连接上级输出,另一输入端口作为控制端引出。振荡器正常工作时控制端全部置高电平。采用Synplify Pro 7.7综合后的原理图如图2所示。该电路完全可实现图1的功能。

为了保证正反馈,图1结构的非门级联必须是奇数个。图2中的与非门起到反相作用,其他与门则起延时缓冲的作用。可以通过改变门的数量以及选择门的种类(与门、与非门等)改变osc输出端的振荡频率,而不受"奇数"个门的限制,只要保障第一个门得到正反馈就可以产生振荡。而图1的结构必须改变偶数个非门才能达到改变振荡频率的目的,因而图2结构在CPLD芯片中实现时可以节省逻辑资源。控制端oscena[n-1,0]为振荡使能控制端,置高电平时,与非门的输入和输出在缓冲级联链的反馈作用下产生自激振荡,振荡器正常工作;控制端的任意一位置零使振荡器停振。所以oscena既可单独使用,也可互联后作为一个端使用。实验证明,图2结构能够保证门延时的等间隔特性。

2 CPLD片内振荡器的实现和优化

2.1 CPLD片内振荡器的实现

基于上述方法的片内环形振荡器设计有很大的通用性,可在不同CPLD芯片间方便地移植。本文以Altera公司的MAX7000S系列CPLD芯片的实现和测试为例说明。MAX7000S系列基于先进的多矩阵构架设计,采用CMOS工艺制造,容量高达256个逻辑单元LE(Logic El-ement),每16个宏单元组成一个逻辑阵列块LAB(LogicArray Block),速度达3.5ns的管脚到管脚延时,同时支持多种I/O电压标准。

从EDA软件综合后的报告可以看出,图2所示电路中每个门占用了一个逻辑单元。也就是说,电路内LE的延时将作为门的延时tpd,而且需要将振荡使能端引出到I/O引脚,当所实现振荡频率较低时,需要较多的门电路单元,这将占用一定的逻辑和引脚资源,从而降低芯片资源的利用率,所以在低频情况下使用时,要综合考虑系统需要的振荡频率,尽量用较少的门电路实现环形振荡器,以提供较高振荡频率,再设计分频电路以取得合适的振荡频率,从而提高芯片的资源利用率。综合器的这一处理,从客观上保证了设计者可以选择不同的门来实现图2的结构,仍然可以保证振荡间隔的一致性。实验也证实了这个结果。

2.2 电源电压的影响

电压会影响振荡电路的工作频率,电压增大会导致电路振荡频率增加,反之振荡频率减小。CPLD芯片一般有两个相对独立的供电端口,即核心电压(VCCINT)和引脚电压(VCCIO)。其中核心电压给芯片内部可编程逻辑电路资源提供电源,引脚电压为芯片的I/O引脚提供电源,以适应各种输出标准(如LVCOMOS、LVTTL、SSTL-2、SSTL-3等)。对振荡频率有影响的是CPLD芯片的核心电压,对此电压应采取稳压措施,稳压措施要视不同的应用要求而定。最简单的措施是采用高性能的稳压芯片给CPLD芯片分别提供两部分电压。随着半导体技术的发展,简单而廉价的稳压芯片已具有较高的性能,如NaTIonal公司的LM2678系列芯片在有效输入变化范围内,稳压输出误差在±2%以内。

2.3 CPLD片内振荡器优化

通过EDA软件对设计做优化有可能提高所设计的振荡器的性能,减少对CPLD片内资源的占用。当采用MAX+plusII10.2软件设计时,软件优化开关设置为:(1)本设计选用MAX系列芯片,故选择对该芯片的多层综合选项(MulTI-Level Synthesis for Max5000/7000/9000De-vice)。(2)在面积和速度优化选项中,选择对面积的优化,使振荡器部分尽可能分配到同一个LAB中。(3)打开"Slow Slew Rate"以降低开关噪声,打开"XOR Synthesis"以减少芯片面积的占用。

3 电路仿真及测试结果

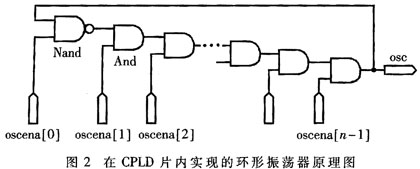

本文以Altera公司的MAX+plus II 10.2为设计工具,在MAX7000S系列芯片上实现并测试。图3为选用EMP7128LC84-15芯片的时序仿真结果。其中p0~p7分别为环形振荡电路中单个门之后的电路节点;oscena[7…0]为各延时门电路的控制端(即所有二输入门中多余的输入端)。

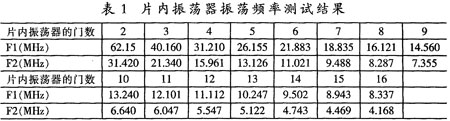

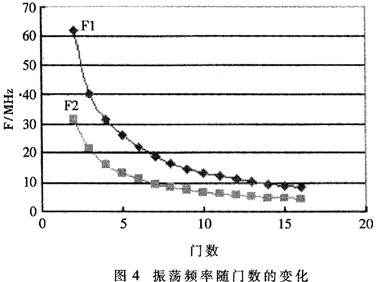

表1列出了以EPM7128LC84-15为目标芯片、采用Tektronic TDS2012示波器对用不同门数实现的片内振荡器的测试数据。F1和F2分别表示片内振荡器输出和二分频输出的测量数据。图4给出了测量数据的曲线。

表1数据表明,通过增加门电路的数量可以有规律地减小振荡电路的工作频率,由每个逻辑单元实现的门电路单元延时tpd在7.5~10ns之间。

本文介绍的基于CPLD的片内振荡器设计方法,在改变该振荡器电路中门电路数量时,可以有规律地将振荡频率控制在8MHz~62MHz范围内。振荡器的片内设计使基于CPLD的片上系统(SoC)设计无需外接时钟信号源,加大了系统的集成度并降低了设计成本。本方法有很大的通用性,可以方便地在不同CPLD芯片间移植。仿真和测试数据表明该设计方法具有正确性和可行性。 欲了解更多信息请登录电子发烧友网(https://www.elecfans.com)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)