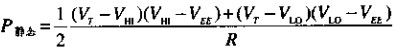

用来计算TTL集电极开路输出电路静态功耗的公式如下:

其中:VT=上拉电阻的有效端接电压

R=端接电阻的有效值

VHI=高电平输出(通常等于VT)

VLO=低电平输出

VEE=输出晶体管的射极(或源极)的电源电压

P静态=输出驱动器的功耗

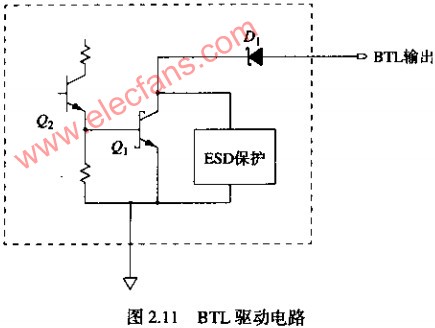

BTL系列的收发器使用集电极开路驱动器,上拉电阻与+2.0V相连。逻辑工作电平为+2.0V和+1.0V。BTL驱动电路包含一个肖特基二极管(见图2.11中的D1),与它的输出引脚串联。当Q1截止时此二极管反向偏置,形成一个非常低的输出电容,典型值为6.5PF。低输出电容是BTL技术的主要优势。

在三态时,推拉输出电路总是用一个反向偏置的基极-发射极PN结与线路相连。PN结的结电容必须足够大,以便能提供大的输出驱动电流,它远远大于一般的输入电容。与之相反,BTL驱动电路在转为OFF状态时的电容非常小。

本文地址:https://www.elecfans.com/arTIcle/analog/2010/20100601218778.html

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)