功能强大的可编程逻辑平台使得Prisma Engineering公司能够针对所有蜂窝网络提供可重配置无线测试设备。长期演进(LTE)是移动宽带的最3GPP标准,它打破了现有蜂窝网络的固有模式。LTE与前代UMTS和GSM标准相比,除采用高频谱效率的射频技术外,其架构还得到了大幅简化。LTE系统的无线接入部分Node-B,是连接无线电和整个互联网协议核心网络之间的边缘设备。这种架构无法监测和测试等效于UMTS中间链路上的元件。必须通过无线电接口,才能有效地测试LTE网络元件。

这正是Prisma Engineering公司线路服务器单元(LSU)UeSIM LTE项目的设计组要解决的问题。该仿真器是针对所有LTE测试需求的全面解决方案,可帮助网络设备设计人员对空中接口和核心网络进行测试和监控。单个这种硬件平台即可在每个扇区模拟出多达1 024个用户设备。无线电接口的载荷-应力测试和功能测试覆盖了完整LTE协议栈及其应用。射频前端采用本地多输入多输出(MIMO)设计,可支持5MHz、10MHz、15MHz和20MHz多种不同带宽。

这个仿真器中心采用三个赛灵思Virtex®-5 FPGA(XC5VSX50T),可支持高级软件无线电重配置。总部设位于意大利米兰的Prisma Engineering公司的设计组很快认识到,我们需要功能强大、可重编程的架构,以便能够用同一开发板灵活应对多种无线接入标准。现有两种用户测试工具:LTE Test Manager(主要针对LTE设备厂商提供)和Quick GUI(主要针对LTE网络营运商提供)。Quick GUI提供通过/未通过测试方案,而Test Manager则可进行更为复杂的分析。

LSU UeSIM LTE架构

LSU UeSIM LTE仿真器采用由协议处理单元(PPU)模板、软件无线电(SDR)模板和支持MIMO *** 作的两个无线电模块共同构成的CompactPCI标准架构。

采用Intel技术的PPU模板是一种主处理器卡,能够对多个SDR模板进行管理,改善载荷-应力性能。软件无线电模板专为扩展我们先前的LSU系统在无线电接口的运行性能而设计。CompactPCI无线电夹层卡负责提供各个不同标准射频带宽的射频发送/接收功能:GSM(850 MHz和900MHz;1.8和1.9GHz)、LTE(700MHz,2.1 GHz、2.3 GHz、2.5 GHz和2.6GHz)和WiMAX(2.4GHz、3.5GHz和5GHz)。

SDR卡架构

SDR卡是一种集成在LSU软/硬件环境中的高性能平台,用于提高系统与基带(CPRI/OBSAI)、无线电接口或者两者之间的连接功能。该卡使用工作在特定频带内的不同外部无线电模块,可支持各种无线标准,比如GSM/EDGE、UMTS、HSPA、WiMAX和LTE等。图1为在LTE测试场景中,仿真器或取代无线电扇区,或为核心网络提供测试接口。

图1 LTE测试场景

我们采用三个德州仪器的1GHz DSP(我们选用了TMS320C6455)和Analog Devices公司的模数转换器(AD9640)与数模转换器(AD9779),完成了基于赛灵思FPGA的SDR卡设计。时钟网络采用Analog Devices公司的AD9549,能够为转换和数字信号处理器件(FPGA、DSP)提供极高的灵活时基。

LTE加工数据通路

Prisma把LTE加工数据通路分为两大部分,一是在FPGA内实现的射频前端。二是在DSP内实现的物理资源分配以及数据通道与控制通道端接。

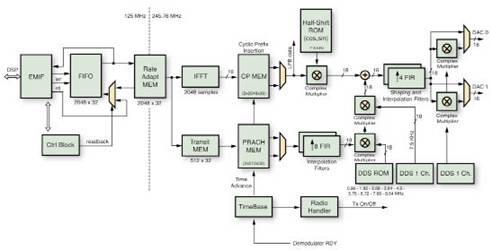

在上行链路方向,由一个DSP负责处理MAC层到物理层的交换以及物理层某些功能的 *** 作。它负责为编码、交织、加扰、符号映射和子载波分配提供参考信号(导频)、源数据和控制通道。离散傅立叶转换(DFT)函数负责根据SC-FDMA标准完成来自不同终端的数据转换。该系统通过EMIF接口把每个OFDM符号都发送到上行链路FPGA。图2为LSU软件无线电卡上的赛灵思Virtex-5 FPGA和TI DSP。

图2 LSU软件无线电卡

该FPGA将数据速率从125MHz(DSP EMIF接口时钟)提升到245.76MHz(FPGA加工速率)。然后FPGA将执行一系列其他 *** 作:2048点反向快速傅立叶转换、循环前缀插入、PRACH数据通道插入、7.5kHz频率下转换OFDM符号频谱的半移位函数、信道整形与内插滤波以及24MHz频率下的中频(IF)转换。随后该器件以122.88MHz的时钟频率把中频数据发送到DAC。同时射频卡将模拟信号转换为射频信号,发送至发射器放大器。下行链路方向上,在LNA放大、可编程增益和转换阶段完成后,射频卡将把接收到的中频数据发送到SDR卡(140MHz)。ADC将以122.88MHz的频率对模拟数据进行二次采样,而FPGA则负责处理最终到基带的17.12MHz频率转换。该数据可以与两个单输入、单输出通道关联,也可以与一个MIMO通道关联。

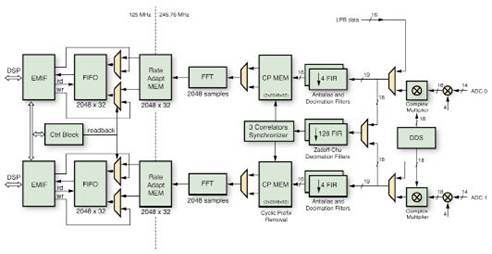

中频数据随后进入下行链路FPGA,由该FPGA将其转换为基带并进行过滤。即便芯片速率保持在245.76MHz,多相抽取滤波器仍能以30.72MHz的符号率进行奈奎斯特FIR滤波、频谱镜像抑制和数据率降低等 *** 作。

FPGA输入数据流看上去像数据流,而非一系列的OFDM符号。同步函数对数据流进行适当的切分,从而描绘出OFDM符号。(要实现这一点,同步线路必须使用多个相关器在深度抽取的输入数据中检测出Zadoff-Chu主同步信号,随即才能获取OFDM符号。)最后,在删除循环前缀后,以FFT转换获得的最终数据则通过EMIF接口传递到另一个DSP。下行链路包含两个以串行RapidIO接口连接在一起的DSP。这两个DSP的作用是进行频率校正、信道估计、均衡和MIMO解码。然后由这两个DSP在MAC层互连之前,进行数据通道和控制通道抽取、Viterbi和Turbo解码、去交织和解扰。

在上行链路侧,由第三个FPGA负责上行链路和下行链路FPGA之间的回送测试,确保SDR模板符合CPRI/OBSAI标准。

我们的设计小组广泛使用赛灵思Core GeneratorTM IP核来生成滤波器、DDS、FFT、Block RMA、FIFO 和MACC功能,把DSP48E和DCM用于设计中的时钟去歪斜部分。这种大规模例化方法在缩短开发时间的同时,还能够提供紧凑设计方案。图3为“上行链路FPGA”实现反向FFT、循环前缀插入、滤波、IF上变频转换以及其他时分双工和PRACH处理所需的 *** 作。该系统将同一信号发送至两个DAC以备冗余。

因为这个项目的市场投放时间要求非常紧迫,我们对其功能划分进行了精心分析。FPGA应该容纳甚至更多的LTE功能,不过我们的设计目标在于寻求系统中FPGA与DSP部分间的平衡。

FPGA设计策略

该项目的市场投放时间要求非常紧迫,因此我们对FPGA和DSP之间的功能划分进行了精心的分析。值得注意的是,FPGA应能够支持更多的LTE功能,不过我们的设计目标之一是寻求系统中FPGA与DSP部分间的平衡。

图3 “上行链路FPGA”

FPGA时钟频率是设计中较为困难的一环。在像调制系统这样的大型设计中采用245.76MHz的时钟速率是项艰巨的任务。我们设计小组需要考虑许多问题,比如功耗、设计约束、布局布线等。尽管如此,由于ISE®设计套件可提供各个设计迭代的稳定高质量结果,过采样因子(FPGA时钟频率与OFDM符号频率之比)为8,能够让诸如滤波器和FFT转换这样的设计项目在尽量少的条件下满足所需的LTE功能。ISE软件也帮助我们实现了合适的同步电路面积。我们设计的关键在于在上行链路中采用射频卡架构(而非存在I/Q不平衡缺点的直接转换法)来接收来自中频的FPGA数据。通过使用赛灵思直接数字频率合成器(direct digital synthesizer),18位正弦/余弦波可用作复杂调制工作的理想载波,并可用在传输无线电信号上测得的误差矢量幅度予以确认。由于采用了赛灵思Virtex-5 FPGA和TI的DSP技术,LSU UeSIM LTE仿真器已经成为蜂窝网络最先进的载荷-应力解决方案测试设备,能为SDR系统提供强大、灵活和可扩展的解决方案。

图4为前端“下行链路FPGA”进行IF下变频转换、多相抽取滤波、同步、循环前缀删除和直接FFT等 *** 作。该系统使用了两个链路来支持TDD和FDD模式的MIMO *** 作。

图4 前端“下行链路FPGA”

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)