以太网是一个占据绝对优势的固线连接标准。Xilinx® Virtex™-5以太网媒体接入控制器(以太网MAC)模块提供了专用的以太网功能,它和Virtex-5 RockeTIO™ GTP收发器以及 SelecTIO™技术相结合,能够让用户与各种网络设备进行连接。Virtex-5器件中,以太网MAC 模块作为一个硬件块集成在FPGA内部。

在Xilinx设计环境中,以太网MAC是一个库原语,名为TEMAC。该原语包括一对10/100/1000 Mbps 的以太网MAC。每个Virtex-5 LXT器件含有四个以太网MAC 模块;因此,一个Virtex-5 LXT设计能够融合两个TEMAC原语。利用标准的Xilinx产品,您可以建立一系列度身定制的数据包处理和网络端点产品。Xilinx还提供了一种超频模式,它能够使底板的连接速率高达2,000 Mbps。

基于Virtex-4 FX以太网MAC,Xilinx开发出了Virtex-5以太网MAC,较之前者,后者在全局时钟使用、串行接口的灵

活性以及软件控制复杂度方面都有了较大的改进。

本文将介绍Virtex-5器件中的以太网MAC模块的功能集,同时描述Virtex-5和Virtex-4 FX以太网MAC之间的区别,指出一

些潜在的应用,探索如何使用标准的Xilinx工具将以太网MAC融入用户的设计。

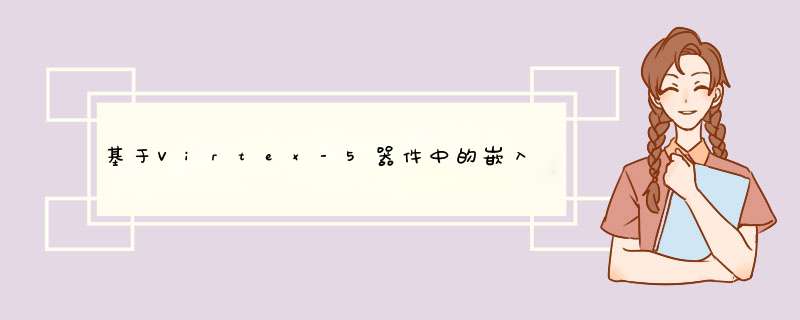

支持的接口Virtex-5以太网MAC完全符合IEEE802.3规范。图1显示了一个以太网MAC的模块结构图。

图1 Virtex-5以太网MAC的模块结构图

物理接口您可以单独配置每个以太网MAC的物理接口,使其作为五种不同的以太网接口中的一种进行工作。

媒体独立接口(MII),吉比特媒体独立接口(GMII)和简化的吉比特媒体独立接口(RGMII)是并行接口。它们通常连接到一个外部物理层(PHY)芯片以提供速率为10/100/1000 Mbps的BASE-T 功能。同时它还支持速率为10/100 Mbps的半双工 *** 作以及各种速率条件下的全双工 *** 作。

串行吉比特媒体独立接口和1000 BASE-X是串行接口,它们使用以太网MAC中的物理编码子层(PCS)和物理媒体接入子层(PMA)部分。它们连接到Virtex-5 RockeTIO GTP串行收发器。当与并行接口一起使用时, SGMII 提供了速率为10/100/1000 Mbps的全双工BASE-T功能。该串行接口大大减少了与外部PHY芯片相连的引脚数量。

当将以太网MAC配置成1000 BASE-X模式时, PCS/PMA模块与RockeTIO收发器一起工作,能够提供与吉比特转换器(GBIC)或者小型可插式(SFP)光纤收发器进行直接连接所需要的所有功能。这可以避免1000 BASE-X网络应用所需的外部PHY芯片。

控制接口主机接口为接入以太网MAC模块配置寄存器提供了通道。配置选项的示例中包括巨帧使能、暂停、单播地址设置以及帧检验序列生成。

客户端接口发送器的客户端接口将帧传送给以太网MAC。当接收到的数据小于最短的以太网帧长度时,发送器将该数据加长,并且保持最小的帧间距;但是,您可以增加间隔的长度,还可以通过配置发送器在帧中添加一个帧检验序列。一个单独的流控制接口允许您生成暂停帧。在半双工模式下,信号发送之间存在冲突,在有效冲突情况下,需要进行帧重发。

接收器接口检验传入帧和信号帧误差。这里分别提供了好帧信号和坏帧信号。还可以通过配置以太网MAC 以便在检测

到有效的暂停帧之后,暂停和重新启动帧传输。

客户端接口的数据的宽度通常是8位或者16位。8位接口主要针对标准的以太网应用,它利用一个125 MHz的时钟产生

1,000 Mbps的数据率。当使用16比特模式时,可以在不提高客户端接口时钟频率的条件下将数据率提高到2,000 Mbps。

每个以太网MAC都会输出一些统计向量,其中含有发送和接收数据通路上所看到的以太网帧的信息。Xilinx CORE

Generator™软件免费提供了一个外部统计模块。该统计模块对每个以太网MAC的发送和接收数据通路上的所有统计信息进行累加。

Virtex-5以太网MAC的新特性在Virtex-4 FPGA中,仅仅实现数据通路就会消耗多达四个全局时钟缓冲器:其中两个分别用于发送和接收客户端接口逻辑,另外两个分别用于发送和接收的物理接口逻辑。在Virtex-5 FPGA中,Xilinx添加了一个时钟使能特性。您可以把生成的时钟用于所有客户端逻辑的物理接口。

内部产生的时钟使能,为在每个接口保持正确的数据吞吐率提供了一个方法。这种方法使所需的时钟缓冲器数目减少了一半。

DCR总线寻址现在Virtex-5 DCR接口为每个以太网MAC提供了一个单独的基地址。这使得共享DCR总线接口对软件驱动程序成为

透明的。软件不再需要知道每个单独以太网MAC的位地址;硬件根据基地址自动选择正确的比特位。

串行接口改动Xilinx对串行接口的 *** 作做了一些改动。随着一个可编程链接计时器的加入,自动检测功能变得更加灵活。您可以在改变自动检测进程时序的同时缩短仿真时间。

新添加的单向模式根据IEEE802.3ah-2004规范执行单向使能功能。一旦使能,不管有效输入是否出现在接收端,以太网MAC都会进行传输。

最后,以太网MAC和收发器可以产生回环。这使得在回环状态中能够将闲置状态传输给链接对象,从而确保该链接保

持活动性。

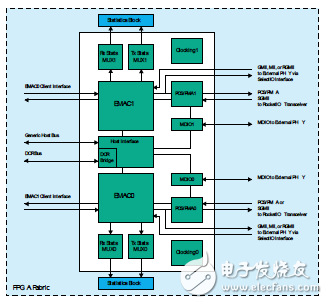

图2 在Virtex-5 FPGA上,MAC连接到一个处理器

Virtex-5以太网MAC使用的模型Virtex-5以太网MAC的多功能性使其可以应用在众多领域。比如,您可以:

• 可以将该以太网MAC连接到一个在网络处理或者远程监测系统中运行协议栈的处理器上,如图2 所示。

• 将以太网MAC连接到一个在 FPGA上实现的数据包处理系统,例如校验和计算及验证的卸载引擎或者远程直接存

储器访问设计。

• 针对数据包的存储、桥接或者交换应用,将多个以太网MAC连接到专用数据包FIFO和外部存储器。

工具和IP支持Xilinx通过CORE Generator软件、LogiCORE™ IP和参考设计对以太网MAC提供支持。

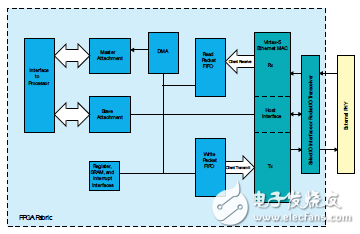

Virtex-5以太网MAC封装图3显示了一个HDL封装的模块结构图,它可以从Xilinx的CORE Generator工具中获得。

图3 Virtex-5 以太网MAC 封装的模块结构图

以太网MAC是一个具有162个端口和79个参数的复杂组件。封装文件使您可以仅对特定应用所需端口的参数和接口

轻松进行设置。它们的另外一个优势是简化了时钟和物理I/O 资源的使用。

分级结构使您可以针对自己的应用抽取正确的封装。

• 以太网 MAC封装。在最低级别,实体化一个单独的或者双以太网MAC,同时在CORE Generator GUI中将它的属性设置成您偏好的选项。所有未使用的输入端口接地,未使用的输出端口保持开路状态。

• 模块级别的封装。在下一层级,对物理接口以及所要求的时钟资源进行实体化。这包括用于串行接口的 RocketIO

GTP收发器。同时针对您的配置对时钟进行优化,并且利用时钟将输出同步到您的设计。

• LocalLink级别的封装。在该级别,将FIFO添加到客户端发送器和接收器接口。FIFO 能够处理接收时坏帧的丢失并

且以半双工模式对帧重新传输。LocalLink 可以作为后端接口使用。

• 示例设计的封装。顶层具有一个演示设计,在这个设计中接收到的数据经过回环重新发送给发送器。您可以将该设计

下载到一个开发板上,然后利用网络设备对该接收器发出激励,从而演示硬件中以太网MAC的 *** 作过程。激励该设计的接收器输入和监视该设计发送器输出的测试台也包含在CORE Generator软件中。

LogiCORE IP和参考设计现有的大部分Virtex-4以太网MAC文档都可以在Virtex-5以太网MAC上重复使用。例如,《以太网内核硬件演示平台》

(XAPP443, )同样适用于Virtex-5以太网MAC。LogiCORE IP,比如以太网统计,已经支持这种新的架构。

结论Virtex-5以太网MAC为各种网络接口提供了一个经济合算的解决方案,使您能够以10/100/1000 Mbps 的速率连接到BASE-X和BASE-T网络。Xilinx的软件工具和IP同样为您充分利用该以太网MAC的改进特性提供了相应支持。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)