0引言

在现代导航计算机系统朝着微型化发展的过程中,采用高性能数字信号处理器和可编程逻辑器件方案实现的导航计算机系统有着很高的性能优势。在本课题组研制的基于浮点型DSP和复杂可编程逻辑器件(CPLD)结构的嵌入式微型导航计算机系统中,DSP负责导航解算任务,CPLD用来辅助DSP对外围通信接口芯片进行控制,以减少DSP的控制任务,使其更专注于导航任务的解算。采用CPLD可以提高导航计算机控制和配置的灵活性,便于系统的升级和更新,使接口配置更灵活,适合于不同的传感器和便于应用于采用多传感器信息融合的组合导航系统中,充分发挥DSP的计算能力,提高导航性能。此嵌入式导航计算机系统中CPLD采用的是Xilinx公司的XC95144,该器件支持在系统编程(InSystemProgramming)和扩展的IEEEStd1149.1JTAG边界扫描测试规范。JTAG标准作为一个测试规范,已被多数可编程逻辑器件采用。对于该芯片的一般编程方法是,通过Xilinx公司提供的下载线缆将PC机并口转接至其JTAG端口,使用PC机下载软件实现对其软件更新。由于JTAG口的信号特点,下载线缆不能太长,否则会导致信号失真;此外,在系统投入使用后,如果需要对软件进行更新升级,采用这种线缆方式必须将系统的外壳打开,不便于系统的维护更新。本文通过对JTAG接口特性的研究,提出了一种采用UART串行通信进行软件更新的方案,对基于DSP接口控制的CPLD器件实现了软件更新,使采用JTAG口进行编程的PLD器件可以实现远端更新和升级。

1JTAG接口原理

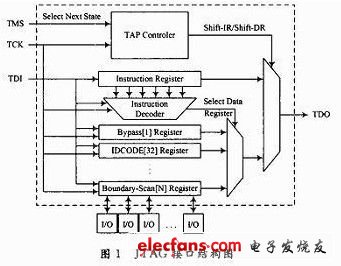

JTAG是IEEE的联合测试行动小组(JointTestAcTIonGroup)提出的测试标准,此标准最初是用来解决因芯片集成度和板级器件密度越来越高带来的测试问题。现在这一标准已被大多数器件厂商采用并设计到芯片电路中,用以支持其器件在系统调试或编程功能。对于本文所用的CPLD器件,其JTAG接口的结构如图1所示。

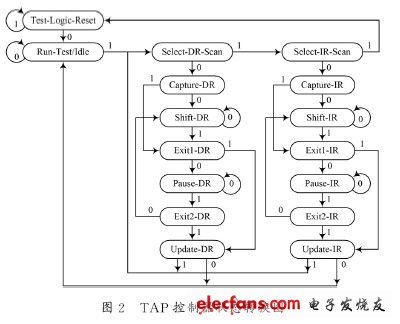

JTAG标准定义了4个基本单元:测试访问端口TAP(TestAccessPort)、数据寄存器、指令寄存器和TAP控制器。TAP端口包含了4个JTAG信号:测试时钟输入引脚TCK,测试数据输入引脚TDI,测试数据输出引脚TDO和测试模式选择引脚TMS。数据寄存器主要包含2种:BYPASS寄存器和BSR(BotlndaryScanRegister)寄存器,其中BSR由BSC(BotmdaryScanCell)串联而成,正是通过BSC扫描链电路,来自于TDI上的CPLD配置信息便可移入到芯片内部,从而实现对器件的擦除与编程功能。TAP控制器其实是一个包含16个状态的状态机,它控制着测试访问口、指令寄存器和数据寄存器。TAP控制器状态转换图如图2所示。

TAP控制器的状态由TMS和TCK两信号控制。当需要将TDI上的数据移到指令寄存器中时,可使TAP控制器进入Shift-IR状态;当需要将TDI上的数据移到数据寄存器中时,可使其进入Shift-DR状态。通过TAP控制器的状态转换,可将CPLD的配置信息移入到其内部逻辑中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)