万物智能强大的连接能力将会把现有无数多个独立的碎片化系统设备连接起来,比特增长的指数现在出现井喷预期。受到数据大规模回流需求驱动,数据中心市场将迎来快速增长机会。

事实上,数据中心应用商机蓬勃。包含云端应用、大数据、智慧交通、智慧城市,车联网、智慧工厂等领域都可透过物联网的布建,达到降低能耗/营运成本、提升 *** 作效率等目标,因此业界正兴起一波建立低功耗数据中心应用模式的风潮;而为了加速推动数据中心的建立,以软件定义的硬件设计平台正挟着低功耗、开放式、易于编程的优势快速崛起。

众所周知,赛灵思在可编程逻辑领域占有领导性地位,此次为了强化数据中心竞争实力,进一步地推出了为数据中心带来最佳单位功耗性能的针对OpenC++L、C和 C++的软件开发环境SDAccel,可有效解决CPU和GPU解决方案较高功耗和性能难以满足需求等限制,进一步满足未来数据中心易于编程、低功耗、高吞吐量和低时延等诸多应用需求。

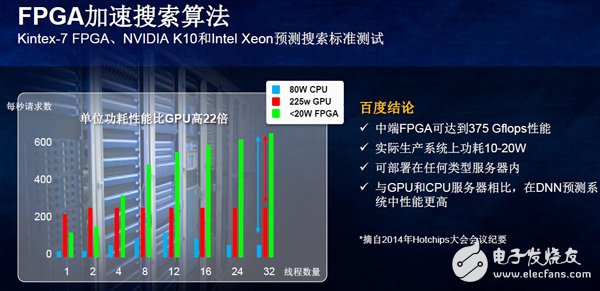

赛灵思公司亚太区销售与市场副总裁杨飞指出,与CPU/GPU相比,赛灵思FPGA方案单位功耗性能最大能提升到25倍。

赛灵思为何看重数据中心这盘生意?

杨飞表示,去年(2014财年)赛灵思营收约24亿美元(包括无线/有线通信和数据中心),在大数据推动下,数据中心有望持续快速成长,未来混合应用场景预计高达10亿美元。

如何克服数据中心严苛的功耗问题?

微处理器厂商竭尽全力地缩减特征尺寸,包括利用新型FinFET工艺,并在CPU中添加特殊的节电状态,但这些仍不足以解决数据中心因集成日趋密集的服务器而造成的功耗危机。实际上负责处理标准因特网流量的大型数据中心一直在努力使功耗预算与电力公司的供电能力保持一致。当增加高分辨率视频、图像识别、深度包检测以及并行算法处理等特殊要求时,就很难让带有标准CPU或GPU的PCI Express开发板将功耗预算保持在25 瓦以内。

中国最大的搜索引擎提供商百度现已转用深度神经网络(DNN)处理技术来解决语音识别、图像搜索以及自然语言处理中存在的各种问题。公司迅速决策到当在线预测使用神经反向传播算法时,FPGA解决方案远比CPU和GPU更容易进行扩展。百度开发的400Gflop软件定义加速,其所用的赛灵思Kintex®-7 480t-2l PCI Express FPGA开发板可以插入到任何类型的1U或2U服务器中。在不同工作负载下,百度发现Kintex 7 FPGA开发板的性能均比GPU高出4倍,比CPU则高出9倍,同时在实际生产系统中功耗仅为10-20W。百度指出应用FPGA解决方案的一大壁垒就是开发时间长,百度建议利用Xilinx SDAccel环境提供的相应软件工具来解决这个问题。

大型数据中心需要令人信服的FPGA实用功能, 微软的案例就是一个有力的证明。在2014年年初,微软启动了一项计划——使用FPGA加速Bing搜索排名。微软公司服务器工程副总裁Kushadra Vaid最近在Linley处理器大会上的一次主题演讲中展示了使用1632台带PCIe FPGA加速卡的服务器试生产结果。相对于未加速的服务器,微软实现方案的吞吐量提高了2倍,而时延和成本分别降低了29%和30%。尽管Vaid展示了ASIC可以提供极高的效率,但他表示他们根本无法赶上快速变化的需求。一直阻碍FPGA在这些数据中心应用中更广泛使用的原因就是缺乏一款高效优化的编译器和相关开发环境,以满足数十年在面向通用CPU和GPU架构的编译器上工作的需求。

杨飞表示,在CPU和GPU单位功耗性能遭遇功耗天花板,为应对数据中心市场带来的严苛低功耗挑战,赛灵思挟SDAccel软件环境、28nm硬件市场优势(全球PLD市场占有率约为71%)、Vivado设计套件和ASIC级芯片技术开发能力,猛攻十万单位量级的小于25W的标准服务器市场。

赛灵思从事特定领域规范环境的开发工作将近十年。数据中心管理人员和服务器/交换机OEM厂商对数据中心性能的关注有助于推动向统一环境纵深发展,从而在数据中心应用中实现设计优化。因此,用于加速的软件定义开发环境SDAccel应运而生。SDAccel的编译器技术建立在赛灵思于2011年年初收购AutoESL时获得的高层次综合(HLS)技术的基础上。赛灵思在过去三年多时间里进一步开发该技术,并将其作为产品供货给1000多名FPGA客户。与此同时,赛灵思还将该技术从针对C和C++扩展到了现在能够优化本地OpenCL代码的编译工作。

为什么是SDAccel?

有越来越多的CPU/GPU厂商、服务器OEM厂商以及数据中心管理员都开始接受OpenCL,这表明各方都认识到了针对单一处理器架构的基于C的优化编译器只能在服务器机架中实现较小的总体功耗削减,即使处理器采用20nm以下工艺并进入特殊的省电模式亦是如此。对于大量使用DSP和图形的应用领域来说,例如数据挖掘与智能、3D可视化,以及微生物学、金融贸易和类似垂直市场中的并行算法开发,一段时间以来这个问题尤为明显。

到目前为止,私企或学术界都未能在统一的FPGA设计充分发挥OpenCL的强大功能。SDAccel开发环境使开发人员可以在x86目标板上执行高效的编译迭代,用自动生成的周期精确内核模型进行仿真,并执行协同仿真与验证。随后,可针对FPGA架构编译优化设计方案。

利用FPGA实现低功耗数据中心不可能一蹴而就。百度、戴尔、微软等公司对新设计方法的推广将有助于提升新型异构服务器的认知度,同时,HSA联盟将在OpenCL使用标准化过程中起到类似作用,或许会在几年内使并行语言成为标准语言。

不过,要发挥OpenCL FPGA的最大效用,需要的不仅是目前所提供的点式编译工具。SDAccel不仅使加速内核接近传统CPU和GPU,甚至超越它们以往的性能,而且还能简化面向未来低功耗异构数据中心的FPGA产品的开发工作。

还有一点可能大家都比较关注的,那就是对于已习惯于CPU或GPU开发环境平台的工程师专家们,SDAccel是如何解决平台过渡的问题的?

杨飞指出,赛灵思已经想工程技术开发人员之所想,SDAccel软件环境本身就是类CPU/GPU开发环境,因此在开发环境相似前提下,SDAccel将非常容易上手。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)