计算机里存储数据主要有这几个部件:CPU里的寄存器和缓存、内存(内存条)和磁盘,这里我们主要简单讲下寄存器和内存条的基础实现电路。

我们就讲到了晶体管怎么表示0,1,那么自然而然我们就会想到,用晶体管来做存储器,但需要多个晶体管来组成门电路,来实现数据的读/写和存储。基础的与门/非门/或门/异或门在该文里也讲到,但在该文我们只是讲了用这些基础门电路组成了加法器电路从而实现加法运算,那么数据的存储,应该怎么实现呢?

那么存储器应该如何工作呢,首先我们要决定数据存在哪儿,就是存储的地址,其次就是数据要稳定的存在,不能受其他 *** 作的影响。好,在讲下,通过门电路,我们可以实现计算机内的逻辑单元(加法器之类的运算单元也是逻辑单元),逻辑单元可以分为两类:一类不可存储信息的(组合逻辑单元);另一类可存储信息(存储单元)。我们分别介绍和内存相关的几个结构。

组合逻辑

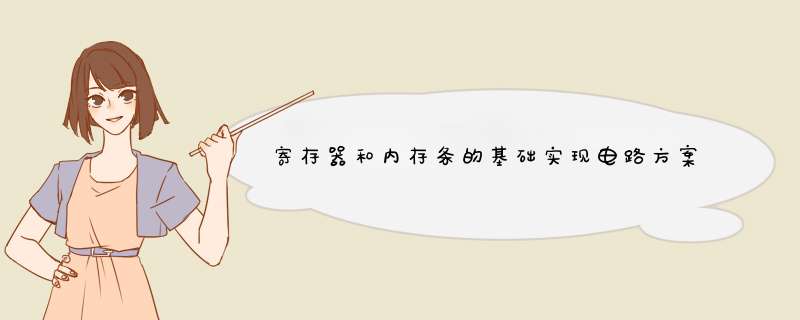

包括各种运算逻辑和控制逻辑,而在存储这块儿,我们需要的是地址选择控制单元,也可以叫地址译码器,它的基本电路如下

依据输入端的二进制(地址值),在输出端选中某一条电路,比如,A=0,B=0,则选中最上面的那条线,A=1,B=1,则选中最下面的那条线

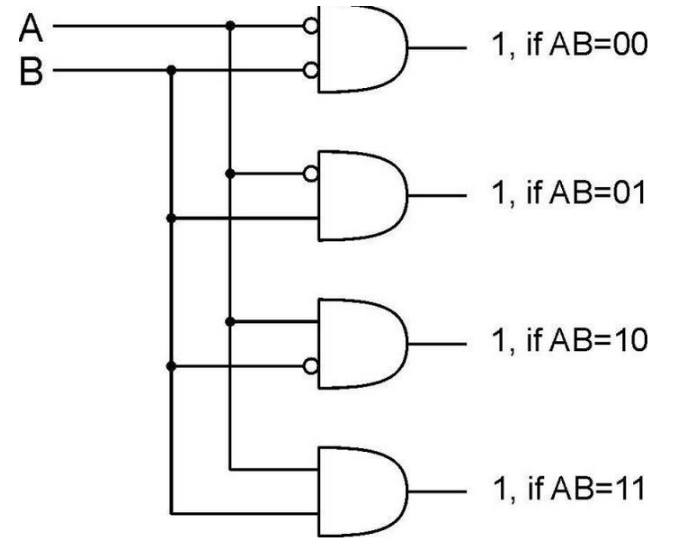

还有就是读出数据的多路复用器:根据控制信号,只选择输入端的某根电路,把这根线输出到输出端

如图,若S1=0,S2=0,则A线路被选中,A的值即是输出值。

存储逻辑单元

可存储信息的结构:可用于保存二进制。

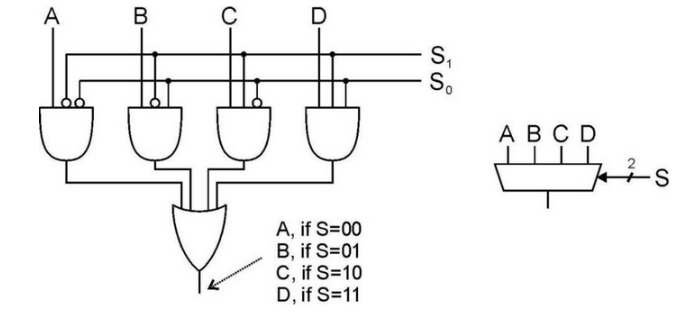

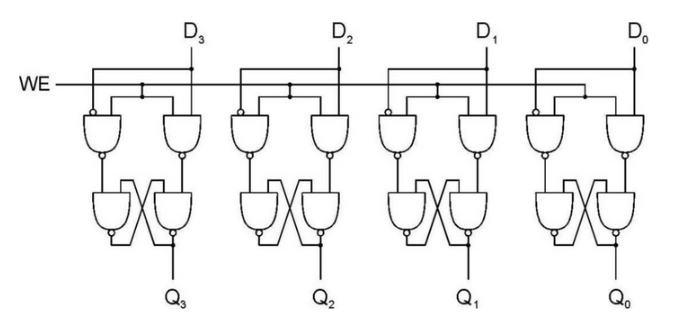

可保存1bit数据的锁存器

WE=0时(不可读写),S和R必为1,则电路稳定,out端可保持原来的值;WE=1时(可读写),则根据D的值,out端变为对应的值。然后恢复WE=0则保存起来

有了1bit的锁存器,我们就可以用n个这样的锁存器组合起来实现n bit的寄存器了

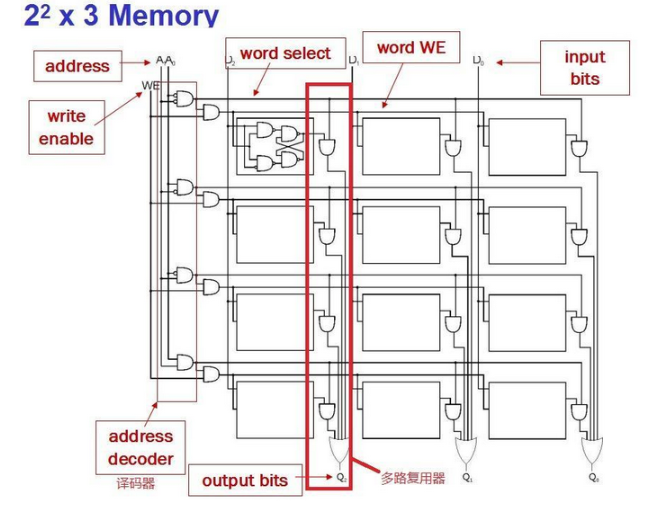

利用地址译码器、多路复用器和锁存器,我们就可以实现简单的随机存储器(RAM)了

如图

内存的寻址由一个2个输入的译码器实现。译码器根据A1和A2的输入,选中对应的一条线,即找到地址对应的存储空间。

内存存储信息的能力具体实现是由门控锁存器组成的存储矩阵保存bit信息。

读取内存的输出由多路复用器实现。根据寻址时译码器选中的某一个线路,每一列的多路复用器只能输出那个线路的对应的那个门控锁存器保存的bit。则最终的三个bit都是由同一个线路对应的三个门控锁存器的输出。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)