SPI 总线接口

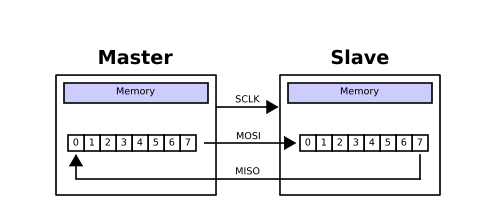

SPI总线主要由4条线组成:

n SCLK —Serial Clock (output from master)

n MOSI/SIMO —Master Output, Slave Input (output from master)

n MISO/SOMI —Master Input, Slave Output (output from slave)

n SS — Slave Select (acTIve low; output from master)

有另一种命名方式也经常可见:

n SCK — Serial Clock (output from master)

n SDI, DI, SI — Serial Data In

n SDO, DO, SO — Serial Data Out

n nCS, CS, nSS, STE — Chip Select, Slave Transmit Enable (acTIve low; output from master)

SPI通讯时Master首先需要配置一个时钟(clock),这个值一般选择小于或者大于Slave设备支持的频率。 通用的频率范围为1-70MHz。

SPI工作在全双工模式,这意味着数据可以在同一时间发送和接收。

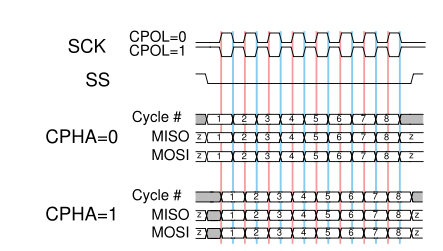

时钟极性polarity与时钟相位phase

时钟极性(CPOL)和时钟相位(CPHA)用于设定从设备何时采样数据。CPOL决定SCLK为高时总线为空闲(CPOL=1)还是SCLK为低时总线为空闲(CPOL=0)。CPHA决定在SCLK的哪一个边沿将数据写入。

按照下面的时序图,

CPOL=0, SCLK为低时总线空闲:

CPHA=0 数据在SCLK的上升沿(rising edge)被读取;数据在下降沿(falling edge)写入;

CPHA=1 数据在SCLK的下降沿(falling edge)被读取;数据在上升沿(rising edge)写入;

CPOL=1, SCLK为高时总线空闲:

CPHA=0 数据在SCLK的下降沿(falling edge)被读取;数据在上升沿(falling edge)写入;

CPHA=1 数据在SCLK的上升沿(falling edge)被读取;数据在下降沿(rising edge)写入;

以下是时序图:

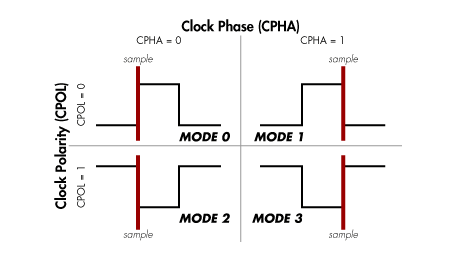

CPOL和CPHA的两个状态允许四种时钟极性和相位的不同组合。每一种都与其他三种不兼容。为了实现主、从设备间的通讯,主、从设备的CPOL和CPHA必须有相同的设置。以下是CPOL,CPHA与4种模式的关系图。

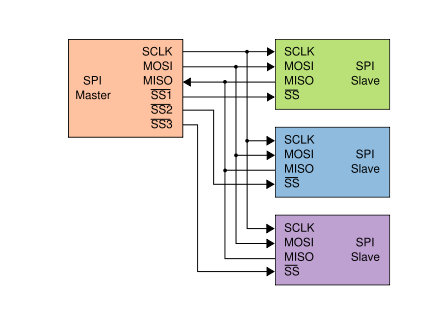

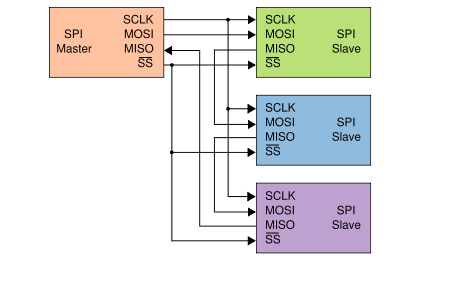

SPI的菊花链配置

一个Master 与3个独立的Slave组合, 每个Slave都有一个独立的SS(Slave Select)。

一个Master与一组使用公用SS(Slave Select)的Slave组合。

以AD7873为例做一些SPI的典型的设置

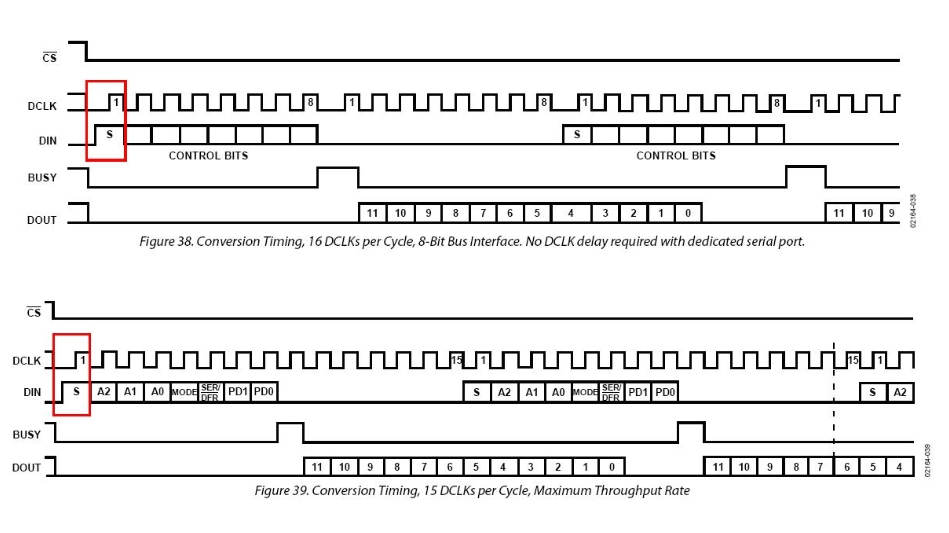

根据时序图,当CS变成低电平时,DCLK为低电平空闲,DIN在DCLK的上升沿数据锁存。所以SPI的polarity与phase设置为Mode 0。

Figure 38 -SPI设置为8bits通信模式,通信周期分为3个阶段:

1》 DCLK前8个DCLK对应指令周期。在这8个DCLK中,通过DIN向AD7873发送8bits命令字控制随后进行的串行数据传输。

2》 数据传输周期从第9个上升沿开始,输入数据在时钟上升沿写入,输出的数据则在时钟的下降沿读出。这里的输入数据为8bits的0数据。DOUT同时也从DCLK的第10个上升沿开始数据输出,到第二个DCLK周期结束时,DOUT输出位数为7bits。

3》 重新开始8个DCLK的指令周期,继续通过DIN传送8bits命令控制字,同时DOUT在第17个DCLK输出最后的5bits数据。

可见在Figure 38中8bits数据通信模式下,AD7873要完成一个完整的SPI数据读写,需要3个周期,即发送24bits数据才能达到目标。

Figure 39 -SPI设置为15bits通信模式,通信周期分为2个阶段:

1》 DCLK前15个DCLK对应指令周期。在这15个DCLK中,通过DIN向AD7873发送15bits命令字控制随后进行的串行数据传输(MSB 8bits为命令字, LSB 7bits为数据0)。DOUT同时也从DCLK的第9个上升沿开始数据输出,第一次15 DLCK周期结束时,DOUT输出位数为MSB 6bits。

2》 重新开始15个DCLK的指令周期,继续通过DIN传送15bits命令控制字。同时DOUT在第16个DCLK输出最后的LSB 6bits数据。

可见在Figure 39中8bits数据通信模式下,AD7873要完成一个完整的SPI数据读写,需要2个周期,即发送30bits 数据才能达到目标。

可见Figure 38使用的DCLK最少,效率最高。不过再8bits传送模式下需要采用连续发送3次8bits数据方式。

如果SPI想在一个周期内一次性将数据读取上来,可以把SPI通信设置为 传送bits》= DIN+DOUT所需的时钟数目,这里根据时序图为22个DCLK。 就可以在22个DCLK中一次性完成写8bits的命令字与读12bits的数据了。不过这里的8bits命令字是22bits中的 MSB 8bits。

不过此方法就没有上面两种通信模式的效率高了。:-)

以Freescale i.mx系列CSPI作为例:

采用CSPI1,POL=0,PHA=0,BIT_COUNT=22

CSPI1_CONTROL.bits.EN=1

CSPI1_CONTROL.bits.MODE=1

CSPI1_CONTROL.bits.POL = 0

CSPI1_CONTROL.bits.PHA = 0

CSPI1_CONTROL.bits.BIT_COUNT= 22

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)