基于FPGA的显示系统有以下优势:第一,LCoS尺寸小,便于实现微投影,利用可灵活编程的FPGA器件作为驱动控制器,这样就可以将其做成像普通投影仪一样的微型投影设备,使计算全息三维显示摆脱了计算机和复杂光路的束缚,具有了更高的灵活性,为其走出实验室提供了条件。第二,因为在传统空间光调制器上得到的图像里含有物波和参考光的复共轭像,形成了噪声,在FPGA上可以实现图像滤波去噪,使得到的图像更清晰。第三,FPGA是基于可编程逻辑单元的器件,当经过综合、布局布线、时钟约束的代码烧录到FPGA器件后,FPGA就将算法代码硬件化了,可以作为专用芯片工作,其内部信号延时完全是硬件级传输延时。在处理数据搬移和复杂的数学运算以及一些循环 *** 作时,例如图像的FFT变换,FPGA硬件运算要比软件运算快得多,即利用FPGA器件实现对软件算法的硬件加速。

基于以上原因,本文设计了基于FPGA的LCoS驱动代码及图像的FFT变换系统,为计算全息三维显示图像处理和显示提供了硬件平台。

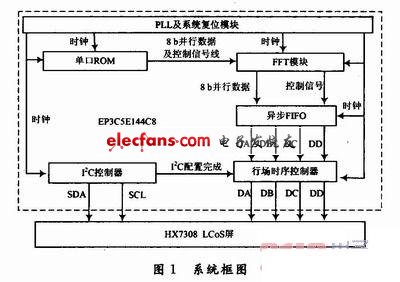

1 系统设计

1.1 系统模块框图:

系统的整体框图如图1所示。

1.2 PLL及系统复位模块

采用Altera的锁相环IP核,外部输入时钟为20 MHz,经倍频后得到其他各模块的驱动时钟,以及LCoS的驱动时钟信号。为防止系统异步复位时寄存器出现亚稳态,设计了PLL的前级和后级D触发器。因为锁相环的locked引脚在锁相环稳定输出后才会跳变为高电平,所以为保证其他模块得到稳定的时钟信号,将locked引脚和外部输入复位信号rst_n相与后作为整个系统的复位信号。

1.3 单口ROM模块

利用FPGA内部的M9K存储器资源实现的单口ROM作为源图像的数据存储器。将分辨率为176×144(QCIF)的256阶灰度位图图像初始化到单口ROM里,所需数据深度为25 344 B。当异步FIFO没写满时,单口ROM将按图像存储地址依次输出图像数据给FFT核做快速傅里叶变换。经过处理的图像数据暂存到FIFO)里,等待行场时序控制器模块取用。

1.4 异步FIFO模块

按其数据地址最高2位分为4个区间,读/写指针分别对某一区间 *** 作,当读/写指针相等时通过译码器产生FIFO已读空或者已写满标志信号。为避免地址信号变化时出现冒险竞争现象,写地址和读地址指针都采用格雷码编码。在读空比较子模块和写满比较子模块里加入了FI-FO“将空”和“将满”检验机制,有效地保证了FIFO正确无误的工作。在写时钟wrclk的上升沿,异步FIFO每个地址对应的存储单元里被写入8bits数据,在读时钟rdclk的上升沿,FIFO四块连续地址上的32bits数据输出,即读FIFO的速率相当于写FIFO速率的4倍速。

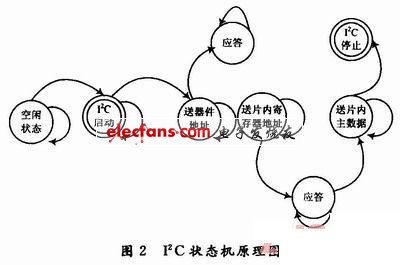

1.5 I2C状态机模块

没有满足I2C配置条件时,状态机处于空闲状态,当满足I2C配置条件时,状态机在状态标志位的控制下依次输出配置地址和配置数据。当数据配置结束时,状态机产生停止信号,并拉高输出引脚iic_config,通知行场时序控制器模块开始工作,这样保证了LCoS屏能在正确配置下工作。状态机工作原理如图2所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)