在软件接收机的研究中,为了实现在GPS或者北斗模式下基带对射频前端数据的采集,在Altera公司的CycloneⅢ系列FPGA器件上采用VERILOG语言编写了SPI总线协议,完成了对射频前端芯片GPS/北斗两种工作模式的切换,使基带可以随时获得两种模式下的数据。通过验证,采集来的数据与期望的结果一致。同时为工程设计提供了一种原型,也为进一步的工程开发奠定了基础。

因此,我们采用ALTERA公司的FPGA器件设计SPI总线的通信接口,该总线接口具有高速、配置灵活等优点,大大地缩短了系统的开发周期。

1 SPI总线原理

1.1 SPI总线协议简介

SPI总线是一种全双工同步串行接口,能够实现微控制器与外设通信。它采用主从模式架构,支持多slave模式应用,并且只占用芯片上四个管脚,节省了芯片的引脚。

1.2 SPI总线接口

SPI是一个环形总线结构,通常有4条线:串行时钟(SCK)线、主机输入/从机输出(MISO)数据线,主机输出/从机输入(MOSI)数据线和低电平有效的从机选择线(CS)。

SPI总线在与外设进行数据交换时,可根据外设的工作要求,配置SCK的相位和极性,从而产生不同的数据格式。如果时钟相位CPFIA=0,数据在时钟脉冲的前沿被采样;如果时钟相位CPHA=1,数据在时钟脉冲的后沿被采样。如果时钟的极性CPOL=0,串行数据的移位 *** 作由时钟的正脉冲触发;如果时钟的极性CPOL=1,串行数据的移位 *** 作由时钟的负脉冲触发。因此,SPI主模块和从模块的时钟相位和极性应该一致。

2 开发平台介绍

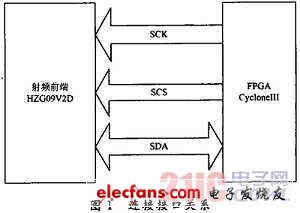

本文主要介绍在FPGA中实现基带对射频前端数据的采集,通过SPI总线实现对射频前端模式的转换。当射频前端被配置为GPS模式时,采集到的数据来自GPS卫星;当被配置为北斗模式时,采集到的数据来自北斗卫星。本文选用的芯片为杭州中科微有限公司HZG09V2D和ALTERA公司Cyclone III系列中的EP3C40Q240C8。接口之问的连接关系如图1所示。

HZG09V2D是杭州中科微有限公司的一款射频芯片,它是一款工作在L1频段的多模式卫星导航射频前端接收芯片,可支持L1频段中国北斗二代、美国GPS、俄罗斯GLONASS、欧洲伽利略等多个导航系统。

EP3C40Q240C8是Altera公司CycloneⅢ系列中的一款FPGA芯片,它前所未有地同时实现了低功耗、低成本和高性能。其中CycloneⅢFPGA在布局上提供丰富的存储器和乘法器资源,并且所有体系结构都含有非常高效的互联。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)