1. 引言

无刷直流电机(BLDC) 用电控装置取代了电刷和换向器,提高了电机的可靠性,并且具有体积小、效率高、噪音低等优点,在消费及工业应用中得到广泛应用。在BLDC控制中,励磁必须与转子位置同步,因此常用一个或多个转子位置传感器确定电机转子相对于电机定子的位置。采用位置传感器的BLDC控制方案较为简单,根据位置传感器的输出确定转子所处的区间,并相应的对电机绕组进行换相。然而,位置传感器的使用会带来一些缺点,如增加系统成本,降低可靠性;同时在一些特殊场合,如在电机处在浸没的环境中,则无法安装传感器。这就要求电机无位置传感器运行。

2. 无传感器控制方案

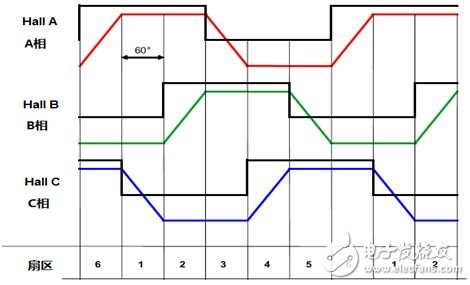

图1即为带霍尔传感器的BLDC换相图。方案采用常规的120°通电方式(六步换相), 为使电机运行,必须按照周期性间隔切换通电的相(即换相)。对于常规通电,每个电周期需要六次等距换相。每一步或每一区间,相当于60个电角度。六个区间组成了360 个电角度或一次电气旋转。每一区间上都有两个绕组通电,一个绕组未通电。要使电机正确换相,必须测量电周期中的绝对位置。采用三个霍尔传感器即可提供六次换相所需要的位置信息。

图1 BLDC换相图

在无传感器控制方案中,必须采用其他方式获取转子位置。转子位置的获得是BLDC无位置传感器控制中的关键技术。常见的转子位置检测有反电动势过零点检测法、反电动势三次谐波积分检测法、续流二极管检测法、磁链估计法等。其中最常用最经典的是反电动势过零点检测法。反电动势过零点检测法不需要详细了解电机特性,可适用于多种电机。

在六步换相过程中,每一区间上都有两个绕组通电,一个绕组未通电。这样在未通电绕组上会出现某相上电流为零,在电机引线上仍可看到电压的现象。这个电压就是反电动势。简单的说,反电动势(EMF)是永磁式电机转子转动时,由定子绕组所产生的电压。反电动势的幅值与电机转速成正比。在图1中,第1扇区中C相电压,第2扇区中的B相电压即为定子绕组产生的反电动势。

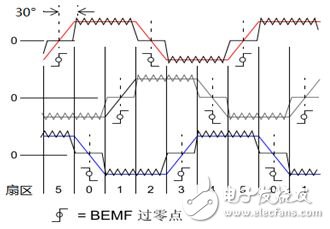

假设电机由±UV 电压驱动,则反电动势信号以0V为中心对称。如果反电动势信号为一条直线,那么信号将在该区间的一半处(也就是该区间的30°电角度处)通过零线。该点称为过零点。在过零事件后再经过30°电角度进行下一次换相。因此,精确检测过零点时刻便可估算转子位置,使电机绕组在正确的时间进行换相。如图2所示。

图2 BEMF过零点与换相图

3. 过零点检测方案

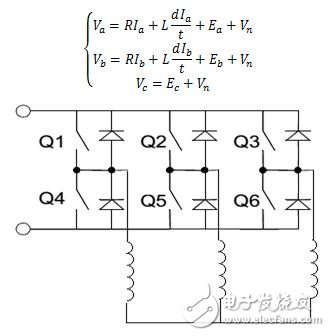

图3 BLDC驱动电路拓扑图

图3为典型的三相BLDC驱动电路拓扑图。假定三相端电压分别为Va,Vb,Vc;Vn为中性点电压;Ea,Eb,Ec为三相反电动势;Ia,Ib,Ic为三相电流,R为相电阻,L为电感。在C相为非导通相时可根据过零点时Va+Vb+Vc=0 及上面等式可得:

3Ec=2Vc-(Va+Vb)

根据以上等式,有三种不同的过零点检测方法:

1.直接用ADC采样三路端电压,根据上述公式判断过零点。此算法需采样多路ADC电压,且需软件滤波算法,对ADC及MIPS均有一定的要求。

2.在 PWM 输出信号为 OFF 时采样非通电相电压,将之与零电压比较。此算法在低速时比较有优势,因为低速时反电势信号比较弱,这种算法的采样区域恰为非通电相端电压过零区域。但当 PWM 的占空比比较高时,由于可供采样的时间点太短,容易造成采样失败。

3.在 PWM 输出信号为 ON 时采样非通电相电压,将之与母线电压的一半比较。此种算法则具有较宽的调速范围,较为通用。

本方案即采用第三种算法进行过零点检测。

4.基于PSoC 4的设计方案

PSoC 4 简介

PSoC 4 是基于ARM Cortex-M0 CPU的可编程嵌入式系统控制器家族,它集合了可编程模拟资源、可编程内部互联、用户可编程数字逻辑、通用的固定功能外设计以及高性能的ARM Cortex-M0 CPU子系统。相对于PSoC3、PSoC5系列产品的各个方面, PSoC 4都做了很大的改进。PSoC 4现包含CY8C4100 和CYCY8C4200两个产品系列,PSoC4100系列是基于ARM内核的最低成本的PSoC,它将PSoC的灵活性和高集成度引入对成本敏感的大批量生产的产品中。PSoC4200系列拥有速度更快的处理器,更高的ADC采样速度,以及基于PLD的增强型通用数字模块(UDB)。以下概括了其主要特性。

● 高性能 Cortex-M0 CPU 内核。基于48 MHz ARM Cortex-M0 中央处理器 , 支持单周期乘法。

● 固定功能以及可配置的数字模块。包括四个独立的可支持中央对齐的PWM,支持互补的可编程死区及同步ADC *** 作;两个可工作为SPI/UART/I2C 串行通信接口的串行通信模块(SCB);

● 高性能模拟系统。包括一个支持零开销通道切换功能的12位1 Msps ADC; 两个支持比较器模式及SAR ADC输入缓冲功能的运算放大器; 两个低功耗比较器;一个电容感应(CapSense)模块,提供极佳的信噪比和防水功能;两个电流数模转换器 (IDAC)。

● 高度可编程的数字逻辑。四个可编程数字逻辑模块(UDB),每个包含两个微型的可编程逻辑阵列和一个8位数据运算单元 。

● 灵活可编程的内部互连。

基于PSoC4的无传感器BLDC控制方案

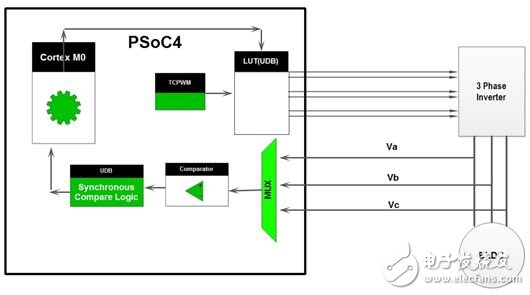

PSoC4 内部集成四个独立的可支持中央对齐、互补的可编程死区及同步ADC *** 作的TCPWM模块;两个支持比较器模式及SAR ADC输入缓冲功能的运算放大器;可完成同步比较逻辑的可编程数字逻辑模块(UDB);可自由切换模拟通道的模拟多路选择器;丰富的片内资源可将主控电路所需芯片集成到一片芯片中,实现高度集成化。图4显示了PSoC4 无传感器BLDC硬件控制框图。

图4 PSoC4 无传感器BLDC硬件控制框图

相对于其他解决方案,基于PSoC4的无传感器BLDC解决方案具有以下特点优势:

1)采用高性价比的Cortex-M0内核。Cortex-M0是市场上现有的最小、最节能的ARM处理器,代码占用空间小,能以8位处理器的价格获得32位处理器的性能,可明显节约系统成本。

2)内部集成两个支持比较器模式及可编程数字逻辑模块(UDB),配合内部模拟多路选择器可无需外部芯片可硬件完成过零点检测,减少系统成本。

3)内部集成两个低功耗比较器,可用于硬件保护或错误信号处理。市场常用解决方案大部分采用外部比较器完成此功能。采用PSoC4可进一步减少BOM,降低成本。

4)通过UDB实现的LUT表硬件实现换相逻辑,较软件方式更加快速可靠。

5)减少PCB空间及BOM成本。由于PSoC4集成了电机控制所需大部分外设及其他丰富的模块,可实现高度集成化的设计。

6)灵活的通讯接口。PSoC特殊的可编程架构提供了极为灵活的通讯接口,可满足各种应用的需求。

基于PSoC4的设计实例

1)原理图设计

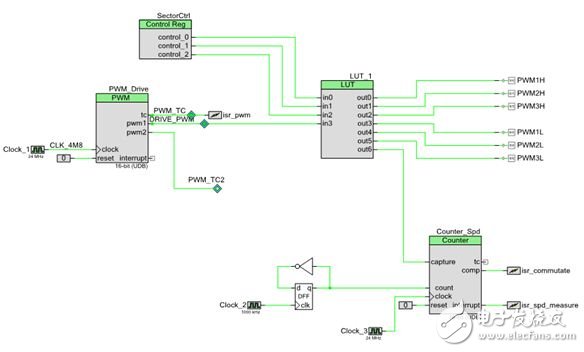

根据图4的控制框图,我们设计了图5及图6所示的BLDC控制原理图。

三相端电压通过IO与内部模拟多路选择器相连,模拟多路选择器会根据换相状态动态的切换所要采样的非通电相并连接至片内比较器。片内的比较器与母线电压的一半比较,输出信号连接至D触发器的输入端。D触发器的的时钟信号来自于数字模块中的PWM模块的输出。 这样通过D触发器可获得在PWM为高电平的时刻端电压与半母线电压的比较结果。而比较器的翻转时刻即是反电势过零点。比较器的输出翻转时,可以触发中断,通知CPU作相应的处理。同时片上的比较器还具有滞回比较的功能。即比较器输出器自上而下翻转与自上而下翻转的电压并不完全一致,而是有一个10mV左右的滞回电压。此功能可以避免比较器输出受毛刺影响而被误触发。

图5 过零点检测原理图

在过零点中断中,CPU可直接通过控制寄存器控制UDB换相逻辑表LUT直接驱动三相全桥电路,完成电机的硬件换相。同时换相信号也同步输入至定时器,完成电机速度检测。

图6 PWM及换相逻辑原理图

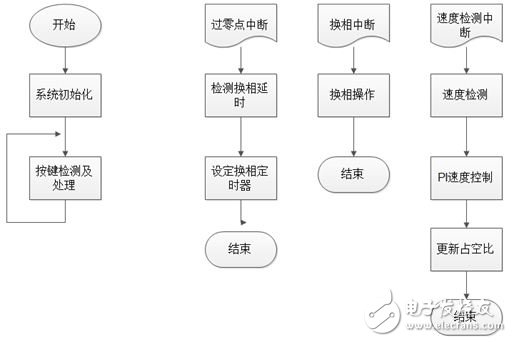

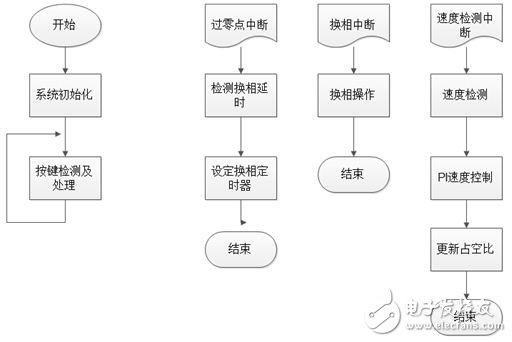

2)程序设计

主程序首先初始化和配置PSoC4的内部资源,在主循环中首先检测按键的启停命令,执行相应 *** 作。根据图5及图6可知,程序主要有三个中断:过零点检测中断、换相中断、速度检测中断。在过零点检测中断中,程序主要完成换相延时的计算及换相定时器的设定;换相中断主要完成LUT控制寄存器的 *** 作完成换相逻辑;速度检测中断主要完成速度检测机PI控制。相关流程图如图7所示。

图7 程序流程图

实验结果

在PSoC Creator环境下编译工程,并连接PSoC4开发板,三相全桥驱动板与BLDC电机,通电后电机可正常运行,图8显示了电机运行时的三相反电动势波形。可以看出,BLDC运行平稳,反电动势为标准的梯形波。

图8 三相反电动势图

5. 小结

上述实例介绍了如何在Cypress新一代可编程片上系统芯片PSoC 4 平台上实现无传感器BLDC控制方案。PSoC 4内部独特的模拟多路选择器、可编程数字逻辑模块配合内部比较器模块可实现灵活的硬件过零点检测方案。同时PSoC 4内部集成的可编程UDB可将换相逻辑以PLD的形式固化在芯片中,实现快速可靠的硬件换相。PSoC 4作为Cypress最新推出的产品,针对电机控制做出了富有特色的优化。凭借片内丰富的资源及高度的灵活性,用户可以轻松设计出高度集成化、低成本、性能优越的电机控制方案。

推荐课程:

张飞软硬开源,基于STM32 BLDC直流无刷电机驱动器视频套件

https://t.elecfans.com/topic/42.html?elecfans_trackid=fsy_post

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)