Cypress在2013年第二季度推出了新一代可编程片上系统PSoC4系列产品,作为PSoC(Programmable System on Chip)芯片家族中的一员,PSoC4保持了Cypress具有特色的片内可编程数字资源和丰富的模拟资源,同时由于采用ARM Cortex-M0作为处理核心,其运算性能也有显著提高。PSoC4内含许多独具匠心的功能模块,逐次逼近式模数转换器(Successive ApproximaTIon Register Analog Digital Convertor,以下简称SAR ADC)就是其中之一。本文即以SAR ADC为例,介绍如何使用PSoC4实现产品设计。

PSoC4简介

PSoC4现包含CY8C4100和CYCY8C4200两个产品系列,均采用ARM Cortex-M0作为处理核心。PSoC4具有灵活的可编程和可重新配置的模拟、数字模块,结合芯片内部灵活的互联网络,可以使用一块芯片实现复杂的混合信号设计。

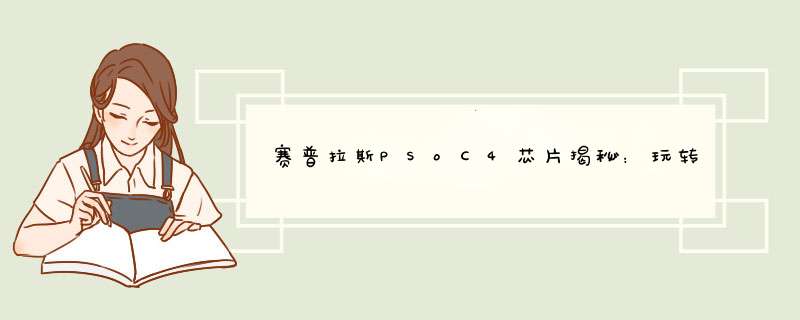

图1是PSoC4的系统框图,以下概括了其主要特性,详细内容可以参考Cypress网站上的PSoC4的数据手册。

● 48MHz ARM Cortex-M0中央处理器,支持单周期乘法

● 最大支持32KB闪存(Flash),最大支持4KB SRAM存储器

● 高达36个可灵活配置的通用输入输出管脚(GPIO),均可配置为触摸感应输入

● 两个可灵活配置驱动能力和带宽的运算放大器,可以工作在比较器模式,也可做ADC的输入缓冲器

● 一个12-bit 1M采样率的SAR ADC,支持差分和单端输入,无软件开销的输入通道切换,硬件实现的采样结果平均,采样结果范围比较

● 两个电流数模转换器(IDAC),不用于CapSense时可以输出给内部模块,或通过GPIO输出用于其他用途

● 两个内部低功耗比较器,可以在深度睡眠和休眠模式下工作,可以产生唤醒信号中断睡眠

● 一个电容感应(CapSense)模块,提供极佳的信噪比和防水功能,具有简单易用的应用设计接口

● 四个通用数字模块(UDB),每个包含两个微型的可编程逻辑阵列和一个8位数据运算单元。Cypress提供了自定义组件功能,用户可以根据设计需要,使用Verilog控制UDB实现用户定制的功能模块

● 2个可灵活配置的串行通讯模块(SCB),每个均可配置成SPI/UART/I2C,支持基于串口的LIN、IrDA、SmartCard协议

● 四个16比特的定时器/计数器/脉冲宽度调制模块(TCPWM),支持中心对齐、边沿对齐模式,伪随机模式,支持灵活的死区控制,PWM可与ADC同步,用户可自定义在PWM周期内任一时刻触发ADC转换),支持同步刷新PWM的占空比

图1:PSoC4芯片系统框图

与 Cypress前一代产品PSoC3/5相同,PSoC4仍然使用PSoC Creator作为集成开发环境。PSoC Creator将硬件资源抽象成了众多的功能模块(Component),每个模块实现一种基本功能,例如PWM模块,I2C模块,基本与门,中断响应模块,输入输出管脚等等。设计者像绘制原理图一样,选择适当模块,将其输入输出与其他模块连接,然后通过每个模块提供的图形化配置向导设置模块参数,之后编写适当的软件代码,即可实现所需功能。这种模块化的设计方法令设计者能够将更多精力集中在实现应用的功能上,而无需关注许多底层硬件配置细节。PSoC Creator的详细使用手册可以在Cypress网站上获得。

PSoC4 SAR ADC模块

与前几代PSoC相比,PSoC4增强了ADC模块的功能。在结构上,PSoC4采用了可获得较高采样速率的逐次逼近式(Successive ApproximaTIon Register,SAR)ADC,能够实现最高1Msps的单通道采样。PSoC4包含一个SAR核心,通过切换采样通道,可以实现多路输入信号的转换。为了减少通道切换对CPU运行时间的占用,PSoC4集成了一个8通道采样输入多路器,提供采样通道硬件切换,从而去掉了通道切换的软件开销。

该多路器最多支持8路单端输入,或者4路差分输入,或者同时包含单端输入和差分输入。图2中实例(a)~(c)分别实现了全单端输入,全差分输入,和单端/ 差分混合输入,如果应用所需的输入信号小于SAR的最大允许值,通过设置SAR的配置可以隐藏未使用的输入通道,如实例(d)使用了两个单端输入通道,此时多路器仅自动切换两个通道,忽略未使用的其余六个通道。

图2:四个SAR设计实例 - 处理单端输入与差分输入

PSoC4 SAR一次完整的单通道采样包含两个阶段:信号获取(AcquisiTIon)和采样转换(ConverTIon)。在信号获取阶段,SAR获得当前输入通道的信号值,储存在内部的采样保持器中;在采样转换阶段,SAR通过不断改变参考电压值,与采样保持器中的信号值做比较,从而将信号值数字化,得到采样结果。PSoC4 SAR的信号获取时间可以由用户设定,而采样转换时间与采样结果位数相关,以1Msps采样率为例,默认的信号获取时间为222.2纳秒,采样转换时间为 777.8纳秒。

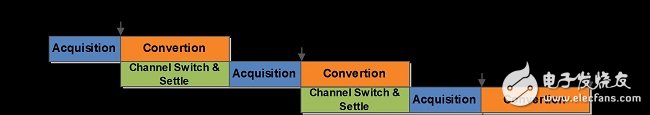

PSoC4 SAR将这两个阶段设计成了流水线的结构,两个阶段之间可独立运行。因而,对于多通道采样,当前输入通道进行采样转换时,多路器可以切换至下一路通道,从而提供一个额外时间对电路中的寄生电容充放电,保证SAR在进入信号获取阶段之前,输入信号已经达到稳定。图3是一个3通道采样的工作示意图,从图中可以看出,PSoC4 SAR在具有较高采样速度的同时,仍有充足时间获得稳定的采样信号。

图3:3通道SAR采样工作示意图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)