本文采用FPGA来设计一款广泛应用于计算机、Modem、数据终端以及许多其他数字设备之间的数据传输的专用异步并行通信接口芯片,实现了某一时钟域(如66 MHz)的8位并行数据到另一低时钟域(如40 MHz)16位并行数据的异步转换,并且客户可以根据自己的要求进行数据定义。完成数据在不同时钟域间的正确传递的同时防止亚稳态的出现,保持系统的稳定,是电路设计的关键。

1 时钟域转换中亚稳态的产生

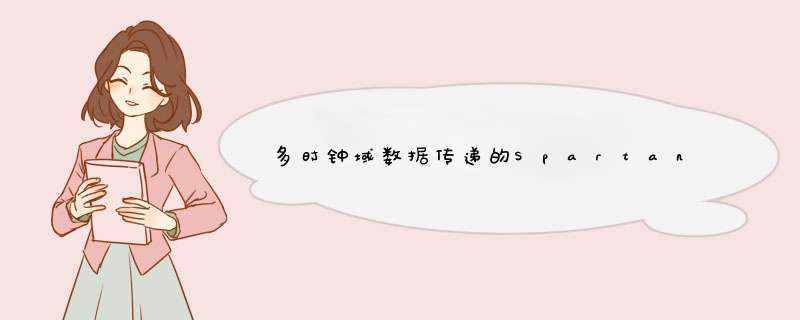

触发器是数字电路设计中的一个重要元件,而触发器工作过程中存在数据建立与保持时间的约束,如果这种约束得不到满足,触发器就会进入某个不确定状态——亚稳态。亚稳态的存在可能导致连锁反应,以致引起整个系统功能混乱。在单时钟域电路设计中由于不存在时钟之间的延迟和错位,所以建立条件和保持条件的时间约束容易满足。而在多时钟域里由于各个模块的非同步性,则必须考虑亚稳态的发生,如图1所示。

2 多时钟域数据传递方案

多时钟域传递的信号有两种,其一为控制信号,其二为数据流信号。针对这两种不同的信号,分别采取不同方案遏制系统堕入亚稳态。对控制信号采用同步器装置,即在2个不同的时钟域之间插入同步器;而对于不同独立时钟域之间的数据流传递,为了避免异步时钟域产生错误的采样电平,采用FIFO存储器作为其转换接口,在输入端口使用写时钟写数据,在输出端口使用读时钟读数据,这样就完成了异步时钟域之间的数据交换。

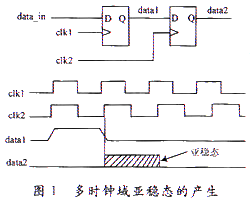

芯片的总体逻辑框图如图2所示,图中输入输出信号定义如表1所示。

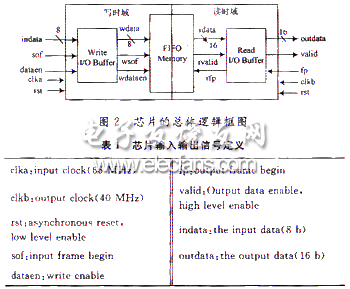

FIFO存储器结构框图如图3所示,他由双端口存储器(Dual Port RAM)、写控制单元(Writc Control)和读控制单元(Read Control)构成。其中DUAL PORT RAM是由ISE6.0的一个编辑软件CORE GENERATER自动生成,使用者只需设定RAM的端口数、内存大小和渎写控制便可以生成一个适合程序的子模块。由于读写时钟属于不同的时钟域,满帧信号Frame从写控制单元向读控制单元传递时必须采取同步器(Synchronizer)同步。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)