0 引 言

本系统以AD7892SQ和CPLD(复杂可编程逻辑器件)为核心设计了一个多路信号采集电路,包括模拟多路复用、集成放大、A/D转换,CPLD控制等。采用硬件描述语言Verilog HDL编程,通过采用CPLD使数据采集的实时性得到提高。

1 硬件设计

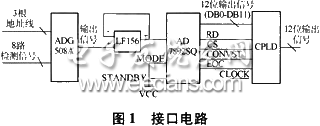

针对多路信号的采集,本系统采用4/8通道ADG508A模拟多路复用器对检测的信号进行选择,CMOS高速放大器LF156对选中的信号进行放大,AD7892SQ实现信号的A/D转换,CPLD完成控制功能。电路如图1所示。

AD7892SQ是美国AD公司生产的LC2MOS型单电源12位A/D转换器,可并行或串行输出。

AD7892SQ A/D转换器具有如下特点:单电源工作(+5 V或+10 V);内部含有采样保持放大器;具有高速的串行和并行接口。

AD7892SQ控制字的功能如下:

a)MODE:输入控制字,低电平时为串行输出,高电平时为并行输出,本系统为并行输出;

b)STANDBY:输入控制字,低电平时为睡眠状态(功耗5 mW),高电平时正常工作,一般应用时接高电平;

c)CONVST:启动转换输入端,当此脚由低变高时,使采样保持器保持开始转换,应加一个大于25 ns的负脉冲来启动转换;

d)EOC:转换结束信号,转换结束时,此脚输出100 ns的低电平脉冲;

e)CS:片选,低电平有效;

f)RD:低电平有效,与CS配合读,使数据输出。

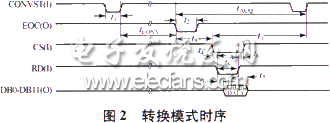

MODE脚接高电平时,AD7892SQ为并行输出,时序如图2所示。

在EOC下降沿时间内开始采样,就是转换一结束就开始下次采样,采样时间fACQ应大于等于200 ns或400 ns,转换结束后(即E0C的下降沿),当CS和RD有效时,经过t6=40 ns的时间,就可以在DB0-DB11上获得转换之后的12位数据,CS和一般的片选信号相同,可以一直有效,外加RD的时间T5也应大于35 ns。CONVST信号t1应大于35 ns,在上升沿时采样保持器处于保持状态,开始A/D转换,转换所需的时间tCONV为1.47μs或1.6μs,转换结束后,EOC脚输出的t2为大于等于60 ns的负脉冲用来进行中断或数据锁存。由此得出下次采样和本次的输出可以同时进行,因此最小的一次采样转换输出的时间为1.47+0.2=1.67μs(600 kSPS(千次采样每秒)),最大1.6+0.4=2 μs(即5 00 kSPS),图2中的t9大于等于200 ns,t7近似为5 ns,t3、t4、t8可为0,(此时t9=tACQ)。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)