引言

随着科学技术和国民经济的快速发展,各种工业生产对电力系统对电能质量的要求越来越高,因此,对电网参数进行实时检测与分析具有重要的意义。要解决电能质量问题,首先要建立电能质量各项指标的监测和分析系统,对电网中的各种指标进行实时更新测量和数据采集。传统的电网数据采集系统往往采用单片机或数字信号处理器(DSP)作为控制器,来控制模/数转换器(ADC)、存储器和其他外围电路的工作。但是,由于单片机本身的指令周期以及处理速度的影响,其时钟频率较低,各种功能都要靠软件的运行来实现,而软件运行时间在整个采样时间中占有很大的比例,效率较低,很难满足系统对数据采集系统实时性和同步性的要求。由于对电网的谐波进行FFT分析时,电网频率不是一成不变的,因此,以固定的采样频率对电信号进行采样时,如电网频率发生波动,采样频率将不能与输入信号同步,因而会产生频谱泄漏。事实上,除了产生频谱泄露以外,对于离散傅里叶变换来说,非同步采样时,即使信号含有单一频率,其离散傅里叶变换也不可能求出信号的准确参数,而会产生栅栏效应。

为了解决这些不足,可在数据采样部分采用高速A/D转换芯片ADS7864,即在数据采集的控制部分则利用FPGA(可编程逻辑器件)直接控制ADS7864对模拟信号进行采样。然后将转换好的12位二进制数据迅速存储到FPGA内部的存储器中。为了提高谐波测量的精度,还可采用硬件描述语言VHDL来设计数字锁相环和同步被测信号,以实现对误差的修正。控制器则根据数字锁相环模块检测出的信号频率大小实时调整A/D转换器的采样频率,以同步被测信号,提高测量精度。

1 设计方案

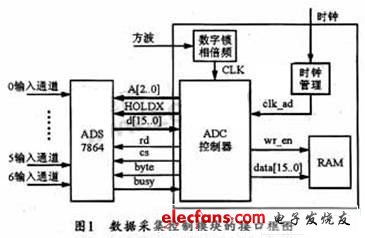

图1所示是本数据采集控制模块的设计框图。图中,数字锁相倍频模块每输出一个有效的采样触发信号CLK,ADC控制器就完成一次6通道的采样 *** 作,然后停止等待下一个触发脉冲的到来。时钟管理模块的作用是利用最小系统板上的50 MHz晶振输入,经过编程进行1000分频,以将其转换成50 kHz提供给AD控制器。至于双口RAM存储模块,由于QuqartusII内部有一个可调用的ROM宏功能模块,因此,在使用时,只要将其调出,并按照本系统的要求对存储容量和地址端口进行设置,就可以作为模块来用。

2 数字锁相倍频

2.1 数字锁相倍频器的基本原理

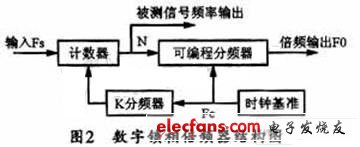

输入信号经整形后可转换为与输入信号同频率的方波信号,其频率为FS,可对其进行K倍频。首先设置一标准的时钟信号,若时钟频率为FC,采用可编程分频器对时钟信号进行分频,其分频系数由计数器提供。若分频系数为N,则输出频率为FC的N分频,即:

时钟信号经K分频后可送至计数器,由计数器在输入信号的一个周期内对FC/K脉冲进行计数,若忽略各种误差因数,其计数值为N,则:

由上两式可得:F0=KFS,这样就实现了对输入信号频率的K倍频,倍频后的信号即可作为A/D的采样信号。数字锁相倍频器中计数器的实质是选用采样窗口信号通过同步过程所得的方波信号作为闸门信号,并将高频率的同步时钟信号作为填充脉冲来进行计数,设计数值为Ⅳ实现周期测量,由于该模块在工作过程中可连续测量输入信号的周期,所以兼有测频的功能。因此,保证数字倍频器跟踪精度的关键是提高周期测量的精度和分频系数的准确度。数字倍频器的原理框图如图2所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)