AD7262具有高速低功耗同步采样,最高可达1 MS/s。其内部集成的可编程放大器PGA有14种放大增益可供选择。两组比较器A、B和C、D用作电机控制或各种电极传感器的运算器。其中比较器A和B具有低功耗特点,比较器C和D具有高速特点。双通道差分输入同时采样和A/D转换,输入阻抗大于1 GΩ。单电源+5 V供电。PGA增益为2,-3 dB带宽为1.7 MHz,信噪比SNR为73 dB;其增益为32时,信噪比为66 dB。输入直流漏电流±0.001μA,失调漂移为2.5μV/℃。带有串行外设接口SPI,兼容QSPI,MICROWIRE,DSP。该器件具有多种节能模式,动态匹配所需内部模块,具有寄存器控制和引脚驱动两种工作方式。

引脚功能

AVcc:模拟电源输入端,4.75~5.25 V;

CA_CBVCC/CC_CDVCC:比较器的电源输入端,2.7~5.25 V;

CA_CB_GND/CC_CD_GND:比较器的地输入端;

VA+/VA-,VB+/VB-:A/D转换器A和B通道的差分模拟输入端;

VREFA/VREFB:A/D转换器A和B通道的基准电压输入输出端;

SCLK:串行时钟,SPI通讯时钟,也是A/D转换过程的时钟源;

CAL:初始化内部失调校准逻辑输入;

PD2:节能模式选择逻辑输入;

PD1:节能模式选择逻辑输入;

PD0/DIN:节能模式选择逻辑输入,同时在寄存器控制模式下为数据输入端;

CS:片选输入端;

CA+/CA-,CB+/CB-:比较器A和B的差分输入端;

CC+/CC-,CD+/CD-:比较器C和D的差分输入端;

AGND:模拟地输入端;

DGND:数字地输入端;

COUTA~COUTD:比较器CMOS推拉输出,使用VDRIVE时,为数字输出端;

DOUTA/DOUTB:A/D转换串行数据输出端;

G0~G3:增益倍数逻辑输入端,当全为低电平时,为寄存器控制工作方式;

VDRIVE:逻辑电源输入端,2.7~5.25 V;

REFSEL:基准电压选择端,高电平使用内部基准电压,低电平使用外部基准电压。

内部结构

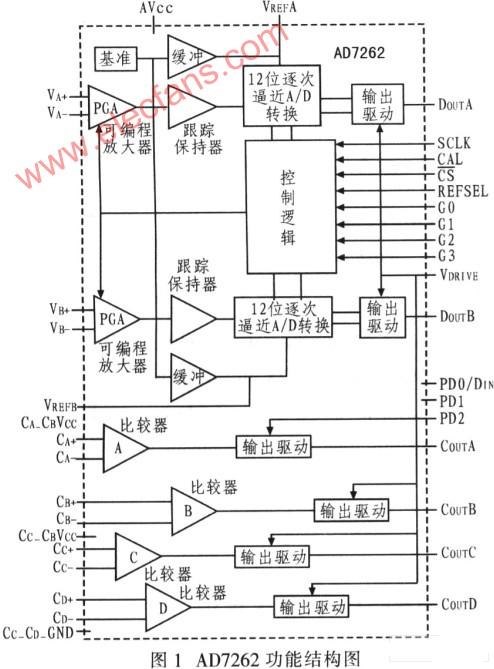

图1为AD7262的内部结构图。两路差分信号通过各自的PGA同步采样放大后,进入跟踪保持器,此时由控制逻辑控制2个12位的逐次逼近型A/D转换器实现模拟数字转换,最后由输出驱动器分别串行驱动输出至DOUTA和DOUTB。

在引脚驱动方式下,G0~G3必须至少有一个高电平。外接的G0~G3决定PGA的放大倍数。PD2~PD0 3个端口电平控制其内部比较器和12位的A/D转换器各模块的使用或关闭。在寄存器控制方式下,PD2,PD1,G0~G3全为低电平。PD0/DIN为数据输入端,用于写入相关控制寄存器,动态配置放大倍数、校准和节能模式。AD7262以2的补码输出转换结果。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)