CAN(Controller Area Network,控制器局域网)总线是德国Bosch公司在20世纪80年代初,为了解决现代汽车中众多的控制与测试仪器之间的数据交换而开发的一种串行数据通信协议。它的短帧数据结构、非破坏性总线性仲裁技术以及灵活的通信方式适应了汽车的实时性和可靠性要求,倍受汽车生产厂商的青睐。随着汽车电子技术的发展,汽车上的ECU(Electronic Control Unit,电子控制单元)越来越多,如电控燃油喷射系统、防抱死制动系统、防滑控制系统等,相应的数据量也越来越大,如何采用合理的存储方案是记录仪等大容量存储系统的关键。本文详细阐述了大容量存储系统系统的整体结构、硬件电路设计。利用“FPGA+单片机”作为存储控制器,采用基于LZW算法的数据压缩技术,以SDRAM作为周期存储和缓存,SD卡作为最终存储载体。实验结果表明,该存储系统可以很好地应用于车载信息记录仪。

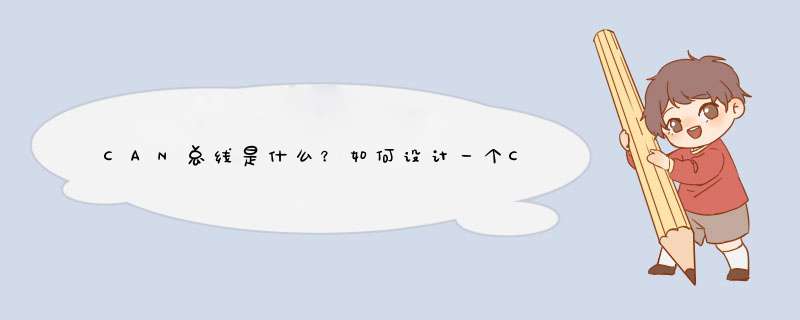

1 系统整体结构设计如图1所示,存储系统主要包括以下模块:FPGA主控模块、CAN总线监听控制模块、数据压缩模块、SDRAM控制模块和单片机控制CH376模块。本文主要介绍存储部分,CAN总线监听控制模块不做介绍。图中,点画线内的部分均由FPGA控制。后端SD卡由MSP430单片机控制,SD协议芯片采用CH376。FPGA控制CAN总线控制芯片、CAN总线收发器从总线上获取数据,经过数据压缩模块压缩,存入SDRAM里。这里采用两种存储模式:一种是利用SDRAM存储的可覆盖性进行周期存储,具体存储周期由压缩率和SDRAM容量决定;另一种是直接存储,SDRAM作为缓存。当选择直接存储时,FPGA与单片机通信,利用FIFO给单片机发送数据,单片机控制 CH376将数据存入SD卡(存储时间由SD卡容量决定)。

FPGA选用Altera公司的Cyclone II系列芯片EP2C5T14418N,它具有内部资源丰富、速度快的特点。上电后,主控模块使能CAN总线监听控制模块、数据压缩模块、SDRAM控制模块。如果选择周期存储,则不使能单片机;若选择直接存储,则让单片机处于低功耗状态,当SDRAM有数据时FPGA把数据发给单片机,并使其控制 CH376工作。

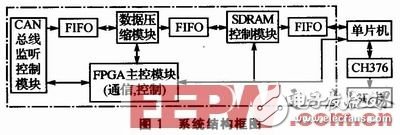

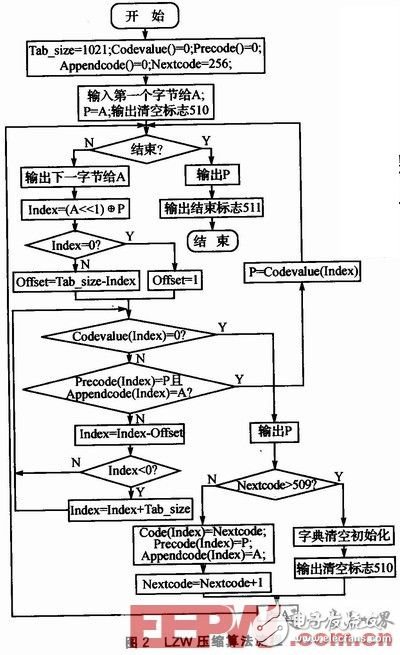

2.2 数据压缩模块压缩算法采用LZW算法。该算法是一种基于字典的压缩算法,在数据的压缩过程中会根据输入的数据动态地建立一个字典。后续输入的数据都会在这个字典中进行匹配查找,根据查找是否成功决定压缩编码的输出。该算法的巧妙之处在于,压缩过程中动态建立的字典不需要与压缩数据流一道进行传输和存储,然而在对数据进行解压时也能够通过压缩数据流重新建立一个字典,来完成解压缩。 LZW压缩算法流程如图2所示。根据该流程,采用C语言设计压缩与解压缩软件以验证算法和硬件压缩的正确性,用Verilog语言编写了压缩代码,利用 FPGA内部RAM资源建立字典。LZW压缩算法的硬件逻辑功能框图如图3所示。

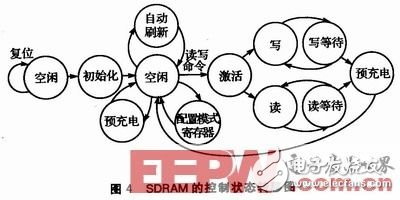

SDRAM(同步动态随机存储器)是一种易失性存储器,以其容量大、价格低的特点得到越来越广泛的应用。但其控制逻辑复杂,需要周期性刷新 *** 作、行列管理、不同延时和命令序列等。图4是SDRAM的控制状态转移图。

CH376是一款国产文件管理控制芯片,用于单片机系统读写U盘或者SD卡中的文件。CH376内置了SD卡的通信接口、 FATl6、FAT32以及FAT l2文件系统等固件,无需自己编写底层协议,控制简单,提供2 MB、24MHz的SPI设备接口,支持连接到单片机的SPI串行总线。CH376应用连接图如图5所示。

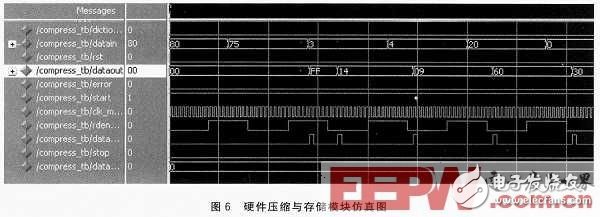

程序编写完之后,利用Modelsim语言仿真软件对其进行仿真。ModelSim能提供友好的仿真环境,是单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,是FPGA/ASIC设计的首选仿真软件。硬件压缩与存储模块仿真如图6所示。仿真结果表明,硬件压缩与软件压缩完全符合。

本文设计了基于“FPGA+单片机”的车载CAN总线采集系统。利用FPGA的优势编写了数据压缩和SDRAM控制两个模块,作为存储系统的核心部分;利用单片机控制能力强、简单的特点设计了SD卡存储控制器,作为数据的最终存储介质,以方便用户在计算机上直接读取数据。实验表明,该系统工作稳定,适合长时间记录数据。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)