关键词:多通道,高速数据采集系统,CPLD,FIFO

1 引 言

随着数字信号处理技术及各种故障分析技术的发展,以及单片机的运算速度的提高,在一些由单片机构成的较小系统中对信号进行实时处理(如谐波分析等)已经成为可能,且越来越受到人们的重视。这就要求作为最底层的数据采集系统,既要具有很高的采样速率,又要能提供更丰富的原始数据信息。

常规采集方案为:(1)由单片机直接控制的采集方案,这是最简单最常用的控制方案。由于每次采样都要有单片机的参与,需占用单片机的时间,影响其数据处理,而且对于多通道、多个A/D转换器的控制,因所需处理的信息更多,则更加不方便。(2)由DMA控制的采集方案。此方案硬件电路复杂,若与单片机配合使用,需要单片机具有总线挂起功能(Hold功能),否则还需要进行总线切换。在总线挂起的时候,单片机就不能访问外部存储器和外部端口,如果单片机要访问外部数据,也只能等待总线的释放,这样就带来很多不方便,也影响数据的及时处理。

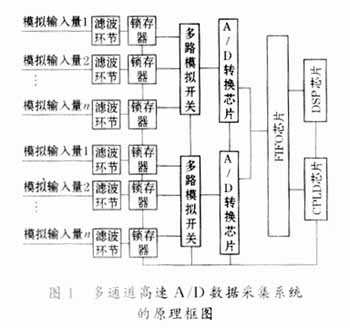

在电力系统的微机检测系统中或者其他数据巡检系统中,需要对多通道的数据作快速的采集分析,尤其是对于实时性很强的系统,更要求采集获得的数据必须实时准确地反映系统的运行情况,例如,故障录波和实时在线监测系统〔1〕〔2〕。本文提出了一种易与各种单片机系统接口的由纯硬件电路控制的多通道高速数据采集系统。它的自动采样硬件电路主要采用CPLD(Complex Programmable Logic Device)和FIFO(First In FirstOut)技术设计而成。该装置可以实现多路模拟量的高速采集,每一个模数转换器(ADC)可以采集10个通道的数据,并且多个模数转换器件的输出可以以总线形式进行扩展。

2 系统设计原理框图和基本设计思想

多通道高速A/D数据采集系统的设计原理框图如图1所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)