作者:Marty Richardson,ADI 高级应用工程师

简介

市场对更高带宽和更高数据速率的需求日益增加,系统频率和调制速率要求不断提高。随着曾经用于军事和国防领域的应用进入消费市场,低功耗变得至关重要。在满足这些要求的同时,还需要保证:不会牺牲电气性能或功能。为了满足这些要求,除了改善进信噪比(SNR)、误码率(BER)和用户熟悉的优质服务外,还必须改善本地振荡器(LO)的相位噪声。

新推出的ADF5610是一款集成式锁相环(PLL)和压控振荡器(VCO),充分体现了ADI致力于解决这些问题最终取得的成果。

频率覆盖范围

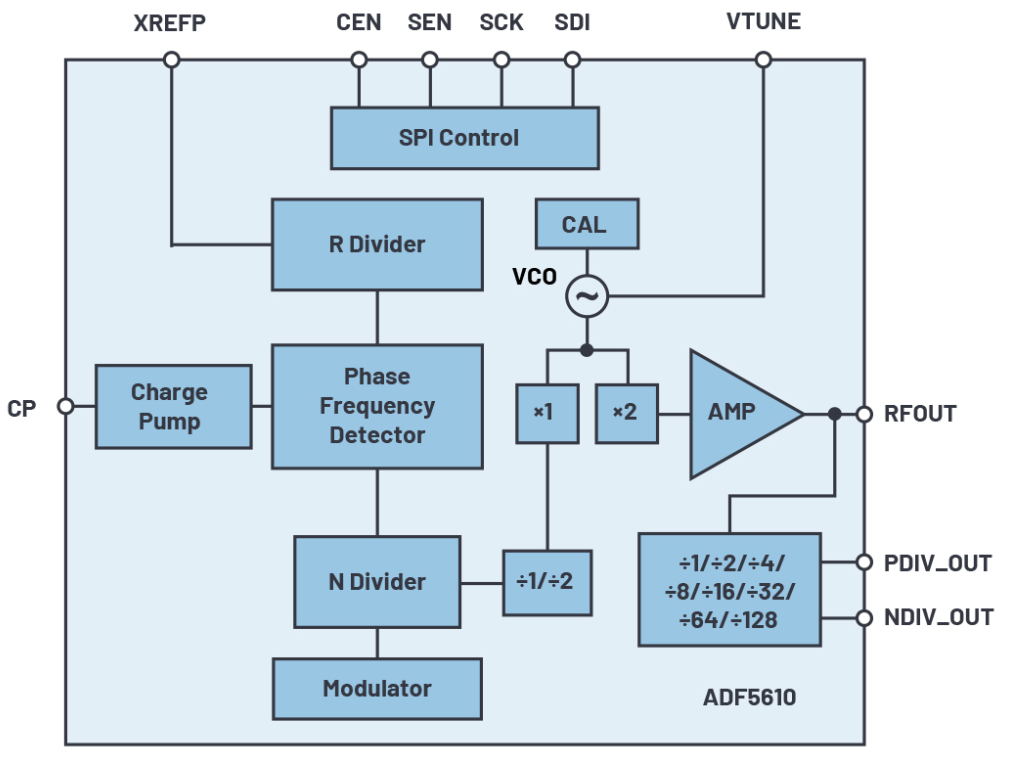

ADF5610总共覆盖8个倍频,VCO基波频率范围为3.65 GHz至7.3 GHz,此频率可反馈给PLL,以最小化相位噪声。单端输出(RFOUT)使基波频率翻倍,可提供7.3 Ghz至14.6 GHz频率,而差分输出通过使用1/2/4/8/16/32/64/128分频设置,同时支持57 MHz至14.6 GHz全频率范围。

图1.ADF5610的功能框图。

ADF5610 的VCO架构可实现出色的宽带频率合成器性能,同时保持行业领先的相位噪声性能,在10 GHz 、100 kHz偏置时,标称开环相位噪声为–114 dBc/Hz。在仅使用一个无源环路滤波器的情况下,内部状态机就可以使频率建立时间低于40 μs;除非需要更快的建立时间,否则无需使用额外的电路或查找表(LUT)。

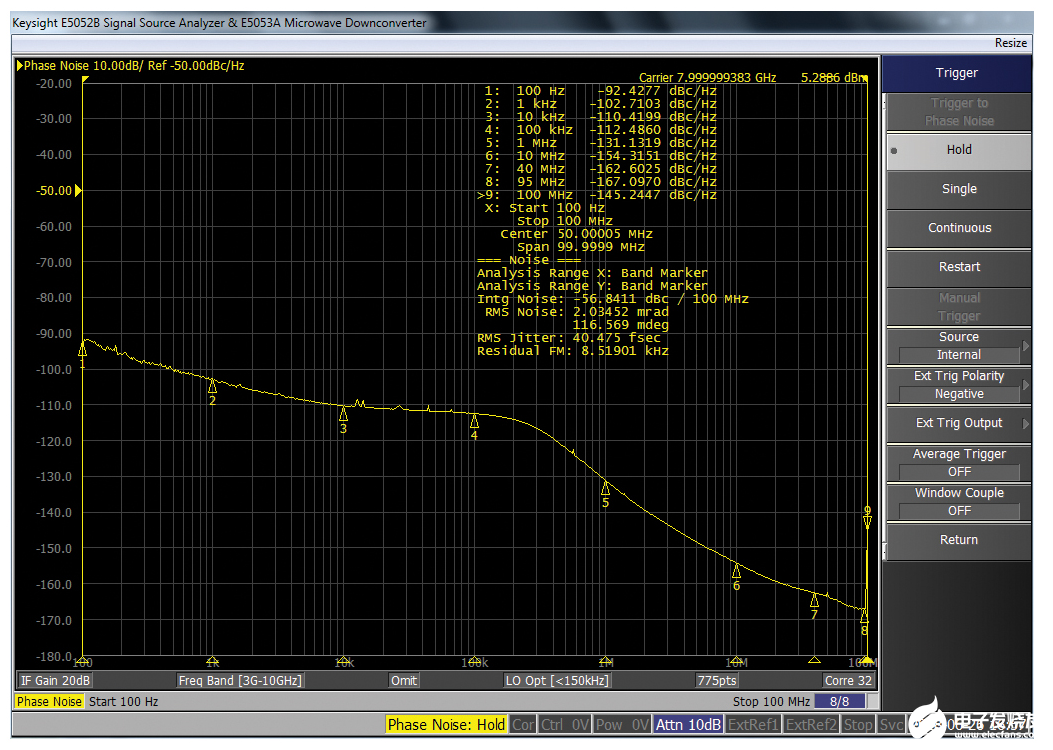

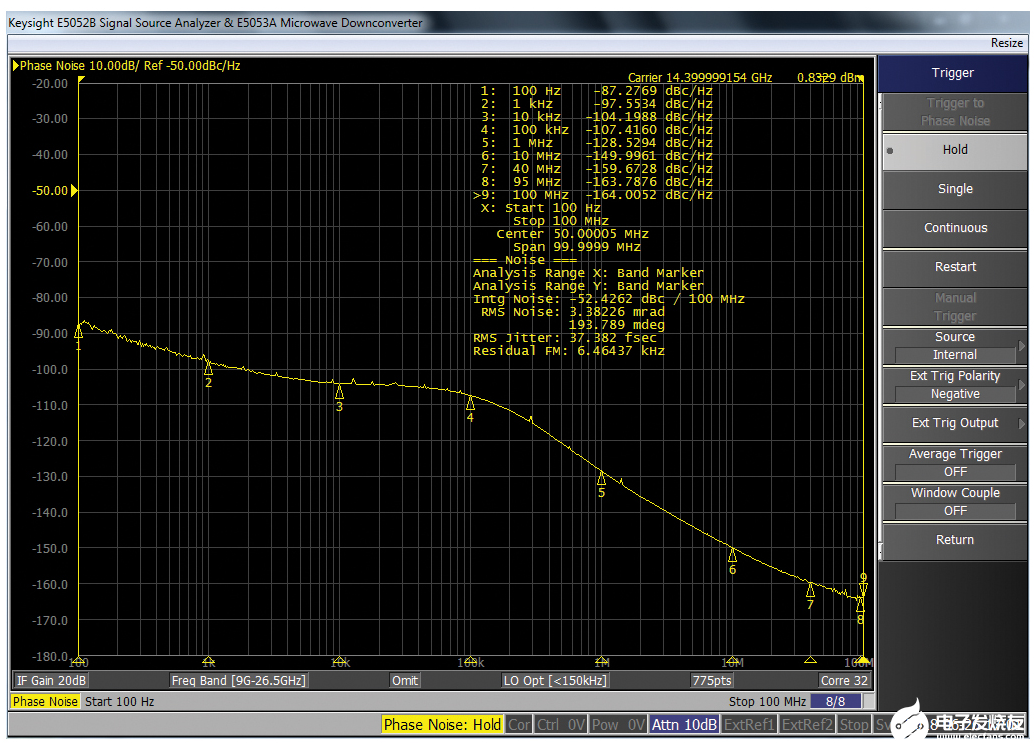

适合转换器时钟应用的出色PLL性能

虽然ADF5610内部的锁相环(PLL)具有中等品质因数(FOM)–229 dBc/Hz(高电流模式下为–232 dBc/Hz),但考虑到1/f噪声(–129 dBc/Hz)和出色的VCO相位噪声特性,则可以实现低于38 fs(1 kHz至100 MHz集成限值)的rms抖动。因此,ADF5610非常适合要求严苛的转换器时钟应用。环路滤波器电阻值应保持最小,以在高频率(100 MHz)范围内实现较低的热噪声。为了达到这个性能水平,必须使用超低噪声基准电压源。

图2.RMS抖动:8.0 GHz。

图3.RMS抖动:14.4 GHz。

通信和仪器仪表LO

除了很宽的频率覆盖范围、行业领先的相位噪声和极快的锁定时间之外,ADF5610还具有其他特性,因此非常适合无线和仪器仪表应用。在这些应用中,ADF5610一般作为本地振荡器使用。

24位小数分辨率相当不错,与ADF5610的精确频率模式功能配合使用时,有可能实现零(0 Hz)误差频率生成。将ADF5610用作本地振荡器时,因为标称输出功率为5 dBm,所以可以直接通过RFOUT端口驱动有源混频器,这样无需额外的放大电路,可以节省宝贵的电路板空间。采用单端方式使用时,差分分频器(PDIVOUT/NDIVOUT)的标称输出功率为2 dBm,但是,在窄带应用中,可以通过低损耗巴伦或混合耦合器将差分进行组合,以实现1~2dB输出功率的增加。

如今低功耗非常重要,ADF5610在低电流模式、禁用输出分频器时,只消耗低于700 mW的功率,即使在最坏情况(高性能模式,输出分频器设为128分频)下,()其功耗稍高于1 W。即使在低电流模式下,ADF5610的相位噪声性能在同类产品中也处于领先水平,仅增加2 dBc/Hz。

ADF5610还具有出色的杂散性能,PFD杂散低至-105 dBc,带内未滤波的整数边界杂散标称值为-45 dBc。

小尺寸

ADF5610 PLL/VCO采用7 mm × 7 mm、48引脚基板栅格阵列(LGA)封装。工作时只需极少的外部去耦,因此可以使用小型解决方案实现出色性能。为实现最佳性能,建议使用优质低压降(LDO)稳压器,例如ADM7150、LT3045/LT3042或HMC1060。VCO需要5 V电源,其余的电路则使用3.3 V电轨供电。ADF5610可以使用ADIsimPLL™进行仿真,以帮助用户设计实现完整的PLL频率合成器所需的适当外部元件电路。

结论

ADF5610具备行业领先的频率覆盖范围、出色的相位噪声性能、高输出功率、低功耗和小尺寸,因此能够满足新通信和仪器仪表系统的严苛要求。

作者简介

Marty Richardson于2014年加入ADI,担任微波频率生成部的高级应用工程师。他在射频/微波领域工作已超过35年,之前曾从事设计和可靠性技术方面的工作。目前,他主要负责锁相环(PLL)、压控振荡器(VCO)和倍频器产品。他是IEEE的高级会员,闲暇时陪伴家人,他喜欢修整家园、打猎、钓鱼和骑山地自行车。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)