引言

锁相环(PLL: Phase-locked loops)是一种利用反馈控制原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。随着集成电路加工中功能器件的尺寸缩小,器件电源电压也呈下降趋势,包括PLL和其它混合信号功能所用的电源。然而,PLL的关键元件——“压控振荡器”(VCO)的实用技术要求并未随之大幅降低。给当今的PLL或RF系统设计师提出了挑战:低压PLL IC如何与高压VCO实现接口。电平转换接口通常利用有源滤波电路来实施,这将在下文讨论。

本文将分析说明PLL的基本原理,考察采用高压VCO的PLL设计的当前技术水平,讨论典型架构的利弊,并介绍高压VCO的一些替代方案。

1 PLL基本原理

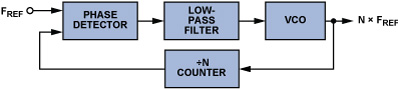

锁相环(图1)是一个反馈系统,其中相位比较器或鉴相器驱动反馈环路中的VCO,使振荡器频率(或相位)精确跟踪所施加的参考频率。通常需要用滤波电路,对正/负误差信号求积分并使之平坦,以及提高环路稳定性。反馈路径中常包含分频器,使输出频率(VCO的范围内)为参考频率的倍数。分频器的频率倍数N可以是整数,也可以是小数,PLL相应地称为“整数N分频PLL”或“小数N分频PLL”。

图1. 基本锁相环

PLL是负反馈控制环路,因此达到均衡时,频率误差信号必须为零,以便在VCO输出端产生精确且稳定的频率N × FREF。

PLL有多种实施方法,根据所需频率范围、噪声和杂散性能以及物理尺寸,可以采用全数字式、全模拟式或混合电路。目前,高频(或RF)PLL的常用架构既含有全数字式模块,如反馈分频器和鉴相器等,也含有高精度模拟电路,如电荷泵和VCO等。

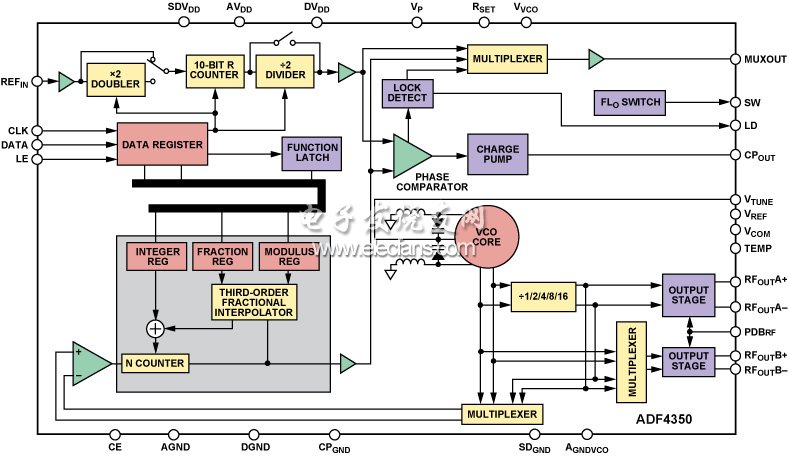

图2显示了当前器件的高度集成电路示例,这是集成VCO的小数N分频PLL IC ADF4350宽带频率合成器的框图,其输出频率范围为137.5 MHz至4400 MHz。

图2. ADF4350 PLL频率合成器框图

限制PLL性能的主要特性有相位噪声、杂散频率和锁定时间。

相位噪声:相当于时域中的抖动,相位噪声是振荡器或PLL噪声在频域中的表现。。

杂散:杂散频率由电荷泵定期更新VCO调谐电压而引起,并以与载波相差PFD频率的偏移频率出现。

锁定时间:从一个频率变为另一个频率或响应瞬时偏移时,PLL的相位或频率返回锁定范围所需的时间。

2 为什么VCO仍然用高压?

高性能VCO是最后几种不为硅集成潮流所动的电子器件之一。仅几年前,手机所用的VCO才完全集成到手机无线电芯片组中。但是,在蜂窝基站、微波点对点系统、军用和航空航天产品以及其它高性能应用中,基于硅的VCO则能力有限,仍然需要采用分立方式来实施VCO。原因如下:

大多数商用分立VCO采用容值可变的变容二极管,作为LC振荡电路的可调谐元件。改变二极管的电压会改变其电容,从而改变振荡电路的谐振频率。

变容二极管的任何电压噪声都会被VCO增益KV(用MHz/V表示)放大,并转换为相位噪声。要使VCO相位噪声保持最小,KV必须尽可能小,但为了实现合理的宽调谐范围,KV必须较大。因此,对于要求低相位噪声和宽调谐范围的应用,VCO制造商通常会设计低增益、输入电压范围较大的振荡器,以满足这些相互矛盾的要求。

3 与高压VCO接口

大多数商用PLL频率合成器IC提供电荷泵输出,其上限约为5.5 V;当环路滤波器仅使用无源器件时,VCO要求较高的调谐电压,该输出不足以直接驱动VCO。为了达到较高的调谐电压,必须利用运算放大器电路实施有源环路滤波器拓扑结构。

实现这种结构的最简单方法是在无源环路滤波器之后添加一个增益级。虽然易于设计,但这种方法有几个缺点:反相运算放大器配置具有低输入阻抗,会使无源环路滤波器承受负载,从而改变环路动态特性;同相配置具有足够高的输入阻抗,不会使滤波器承受负载,但有源滤波器增益会放大运算放大器的任何噪声,从而无法受益于前置无源环路滤波器的滤波功能。

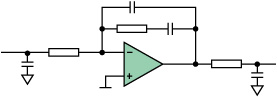

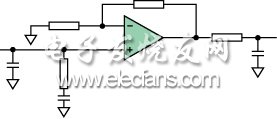

图3显示建议有源滤波器拓扑结构的两个示例,其中前置滤波分别使用反相和同相增益。请注意,这些放大器电路是真时间积分器,可强迫PLL环路在输入端保持零误差。环路之外,所示拓扑结构可能会漂移至供电轨

a. 反相拓扑结构

b. 同相拓扑结构

图3. 采用前置滤波的有源滤波器

反相拓扑结构的优势是可以将电荷泵输出偏置在固定电压,通常为电荷泵电压的一半(VP/2),此时对杂散性能最有利。注意应提供干净的偏置电压,最好是来源于ADP150等专用低噪声线性稳压器,并在尽可能靠近运算放大器输入引脚处充分去耦。分压器网络所用的电阻值应尽可能小,以便降低噪声。使用反相拓扑结构时,必须确保PLL IC允许PFD极性反转;如有必要,应抵消运算放大器的反转,以正确的极性驱动VCO。ADF4xxx系列就具有这种特性。

同相环路滤波器配置不需要专用偏置,因此这种解决方案可能更紧凑。此时,电荷泵电压不是偏置在固定电平,而是在其工作电压范围内变化。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)